| |

Click here for full text:

Defect-Tolerant Interconnect to Nanoelectronic Circuits: Internally-Redundant Demultiplexers Based on Error-Correcting Codes

Kuekes, Philip J.; Robinett, Warren; Seroussi, Gadiel; Williams, R. Stanley

HPL-2004-121

Keyword(s): No keywords available.

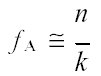

Abstract: Please note: This abstract contains mathematical formula which cannot be represented here. We describe a family of defect-tolerant demultiplexers based on error-correcting codes. A conventional demultiplexer with a k-bit input address and 2k-bit output may be fortified against certain defect types by widening its address bus to n > k bit s to permit an encoded address to be used within the demultiplexer. The redundant address is computed by an encoder that guarantees a minimum Hamming distance d between addresses, which sparsely populate an expanded address space. The increased Hamming distances between addresses are especially tolerant of stuck-open defects (and broken wires, which are equivalent to multiple stuck-open defects). For each address width k, there are a series of demultiplexer designs with increasing internal redundancy, increasing d, and increasing capability for defect tolerance. These circuit designs are especially suitable for nano-scale crossbars; in particular, they may be realized at the interface where the CMOS wires of conventional microelectronics cross nano-wires to form a mixed- scale interconnect crossbar. Thus, a small number (2n) of CMOS wires may be used to control a much larger number (2k) of nano-wires; the family of encoded demultiplexer designs provides a robust interface to the nano-circuitry , giving significant protection from manufacturing mistakes at the cost of a relatively small amount of area overhead  . This a qualitatively new application of error-correcting codes, the analysis of which combines elements of the conventional coding-theoretic notions of full-error and erasure correction. In particular, a code with minimum distance d guarantees tolerance to up to d- 1 defects per nano wire, in analogy to conventional erasure correction. . This a qualitatively new application of error-correcting codes, the analysis of which combines elements of the conventional coding-theoretic notions of full-error and erasure correction. In particular, a code with minimum distance d guarantees tolerance to up to d- 1 defects per nano wire, in analogy to conventional erasure correction.

58 Pages

Back to Index

|