#### **Iterative Modulo Scheduling**

B. Ramakrishna Rau Compiler and Architecture Research HPL-94-115 November, 1995

modulo scheduling, instruction scheduling, software pipelining, loop scheduling

Modulo scheduling is a framework within which algorithms for the software pipelining of innermost loops may be defined. The framework specifies a set of constraints that must be met in order to achieve a legal modulo schedule. A wide variety of algorithms and heuristics can be defined within this framework. Little work has been done to evaluate and compare alternative algorithms and heuristics for modulo scheduling from the viewpoints of schedule quality as well as computational complexity. This, along with a vague and unfounded perception that modulo scheduling is computationally expensive as well as have implement, difficult to inhibited its incorporation into product compilers. This report presents iterative modulo scheduling, a practical algorithm that is capable of dealing with realistic machine models. The report also characterizes the algorithm in terms of the quality of the generated schedules as well the computational expense incurred.

Internal Accession Date Only

÷

Published in The International Journal of Parallel Processing, Volume 24, Number 1, February 1996. An earlier version of this report was published in the Proceedings of the 27th Annual International Symposium on Microarchitecture, San Jose, California, November 1994.

© Copyright Hewlett-Packard Company 1995

# **1** Introduction

.

It is well known that there is inadequate instruction-level parallelism (ILP), as a rule, between the operations in a single basic block and that higher levels of parallelism can only result from exploiting the ILP between successive basic blocks. Global acyclic scheduling techniques, such as trace scheduling [30, 45] and superblock scheduling [37], do so by moving operations from their original basic blocks to preceding or succeeding basic blocks. In the case of loops, the successive basic blocks correspond to the successive iterations of the loop rather than to a sequence of distinct basic blocks.

Various cyclic scheduling schemes have been developed in order to achieve higher levels of ILP by moving operations across iteration boundaries, i.e., either backwards to previous iterations or forwards to succeeding iterations. One approach, "unroll-before-scheduling", is to unroll the loop some number of times and to apply a global acyclic scheduling algorithm to the unrolled loop body [30, 45, 37]. This achieves overlap between the iterations in the unrolled loop body, but still maintains a scheduling barrier at the back-edge. The resulting performance degradation can be reduced by increasing the extent of the unrolling, but it is at the cost of increased code size and scheduling effort.

Software pipelining [14] refers to a class of global cyclic scheduling algorithms which impose no such scheduling barrier<sup>1</sup>. One way of performing software pipelining, the "move-then-schedule" approach, is to move instructions, one by one, across the back-edge of the loop, in either the forward or the backward direction [22, 23, 39, 32, 51]. This is accompanied by the appropriate replication and unification of the operation as it moves past splits and merges in the control flow graph. For instance, if an operation is being moved down and around the backedge (i.e., to the next iteration), a copy of the operation must be made in the basic block following the loop as the operation moves past the split at the end of the loop body. Furthermore, since the operation is moved along the backedge and back into the top of the loop body, it must be matched by and unified with a copy that moves in from the basic block just before the loop. So that such an copy exists, the first iteration of the loop should have been peeled off. If an operation is moved down

<sup>&</sup>lt;sup>1</sup> The original use of this term by Charlesworth was to refer to a limited form of modulo scheduling. However, current usage of the term has broadened its meaning to the one indicated here.

and around the backedge N times, the first N iterations of the loop should have been peeled off. Similar rules apply if an operation is moved speculatively up and around the backedge to a previous iteration.

Although such code motion can yield improvements in the schedule, it is not always clear which operations should be moved around the back edge, in which direction and how many times to get the best results. At some point, further code motion around the back-edge will cease to improve the schedule and, in fact, will cause problems since the register pressure will increase. But it is unclear at what point further code motion becomes unproductive. Since we do not know what the optimal performance is, we could well be striving in vain for improvements that are just not possible, and we might have gone past the optimal point, resulting in reduced performance due to excessive code motion. The process is somewhat arbitrary and reminiscent of early attempts at global acyclic scheduling by ad hoc code motion between basic blocks [71]. On the other hand, this currently represents the only approach to software pipelining that at least has the potential to handle loops containing control flow in a near-optimal fashion, and which has actually been implemented [51]. How close it gets, in practice, to the optimal has not been studied and, in fact, for this approach, even the notion of "optimal" has not been defined.

The other approach, the "schedule-then-move" approach, is to instead focus directly on the creation of a schedule that maximizes performance, and to subsequently ascertain the code motions that are implicit in the schedule. Once again, there are two ways of doing this. The first, "unroll-whilescheduling", is to simultaneously unroll and schedule the loop until one gets to a point at which the rest of the schedule would be a repetition of an existing portion of the schedule [3]. Instead of further unrolling and scheduling, one can terminate the process by generating a branch back to the beginning of the repetitive portion. Recognition of this situation requires that one maintain the state of the scheduling process, which includes at least the following information: knowledge of how many iterations are in execution and, for each one, which operations have been scheduled, when their results will be available, what machine resources have been committed to their execution into the future and are, hence, unavailable, and which register has been allocated to each result. All of this has to be identical if one is to be able to branch back to a previously generated portion of the schedule. Computing, recording and comparing this state presents certain engineering challenges that have not yet been addressed by a serious implementation although the Petri net approach [56, 4] and other finite-state automata approaches [52, 55, 7] constitute possible strategies for kernel recognition. On the other hand, by focusing solely on creating a good schedule, with no scheduling barriers and no ad hoc, a priori decisions regarding inter-block code motion, such

3

unroll-while-scheduling schemes have the potential of yielding very good schedules even on loops containing control flow.

Another "schedule-then-move" approach is modulo scheduling [61], a framework within which algorithms of this kind may be defined. The framework specifies a set of constraints that must be met in order to achieve a legal modulo schedule. The objective of modulo scheduling is to engineer a schedule for one iteration<sup>1</sup> of the loop such that when this same schedule is repeated at regular intervals, no intra- or inter-iteration dependence is violated, and no resource usage conflict arises between operations of either the same or distinct iterations. This constant interval between the start of successive iterations is termed the **initiation interval** (**II**). In contrast to unrolling approaches, the code expansion is quite limited. In fact, with the appropriate hardware support, there need be no code expansion whatsoever [63]. Once the modulo schedule has been created, all the implied code motions and the complete structure of the code, including the placement and the target of the loop-closing branch, can all be determined. (This is discussed further in Section 2.3.)

Modulo scheduling an innermost loop consists of a number of steps, only one of which is the actual modulo scheduling process.

- In general, the body of the loop is an acyclic control flow graph. With the use of either profile information or heuristics, only those control flow paths that are expected to be frequently executed can be selected [43] as is done with hyperblock scheduling [48, 47]. This defines a region that is to be modulo scheduled, and which, in general, has multiple back-edges and multiple exits.

- The early exit branches may either be retained or replaced by a pair of operations: one that sets the loop exit predicate to true, and one that sets a steering variable to a value that uniquely corresponds to this early exit. (By the correct use of the predicated execution capability, only those operations that should have executed, before exiting the loop, will execute.) After exiting the loop, a case statement on the steering variable guides flow of control to the appropriate exit target. In a similar manner, if there are multiple branches back to the loop header, they are coalesced by redirecting them to a single loop-closing branch [48, 47].

ž

<sup>&</sup>lt;sup>1</sup> As we shall see shortly, in certain cases it may be benefical to unroll the loop body a few times prior to modulo scheduling, in which case, the "single iteration" that we are discussing here may correspond to multiple iterations of the original loop. However, unrolling is not an essential part of modulo scheduling.

- Within this selected region, memory reference data flow analysis and optimization are performed in order to eliminate partially redundant loads and stores as was done in the Cydra 5 compiler [59, 20] and in subsequent research investigations [13, 21]. This can improve the schedule either if a load is on a critical path or if the memory ports are the critical (most heavily used) resources.

- At this point, the selected region is IF-converted [5, 54, 20], with the result that all branches to targets within the region, except for the loop-closing branch disappear. With control flow converted to data dependences involving predicates [64, 40, 9], the region now looks either like a single basic block (if the early exit branches are eliminated) or like a superblock [48, 47]. In the event that the target architecture has special branch support for modulo scheduling, the loop-closing branch is replaced by either a **brtop** or **wtop** branch [64, 40, 9], depending on whether the loop is a DO-loop or WHILE-loop.

- Anti- and output dependences are minimized by putting the computation into the dynamic single assignment form [59]. (This is discussed further in Section 2.5.)

- If control dependences are the limiting factor in schedule performance, they may be selectively ignored thereby enabling speculative code motion [70, 46]. In the context of IF-converted code, this is termed predicate lifting; the predicate is replaced by a "larger" predicate, i.e., one that is true whenever the original one is true, but which also is true sometimes when the original one is not.

- Critical path reduction of data and control dependences may be employed to further reduce critical path lengths [66, 20, 67].

- Next, the lower bound on the initiation interval is computed. This is termed the minimum initiation interval (MII).

- If the MII is not an integer, and if the percentage degradation in rounding it up to the next larger integer is unacceptably high, the body of the loop may be unrolled prior to scheduling. The extent of pre-unrolling can be computed quite easily so as to get the percentage degradation down below some acceptable threshold. For a given non-integer MII, f, the degree of pre-unroll, U, is determined by computing the smallest value of U such that the sub-optimality of the effective II, [f\*U], given by the expression ([f\*U]/(f\*U) 1), is less than some threshold of tolerable degradation (for instance, 0.05).

- At this point, the actual modulo scheduling is performed.

ţ

- The register requirements of the modulo schedule may be reduced by performing stage scheduling [27] which moves operations by integer multiples of II so as to reduce lifetime lengths.

- The predicates of operations whose predicates were lifted prior to scheduling are now made as small as possible, consistent with the schedule, in order to avoid unnecessary speculation which can result in increased register pressure. When possible the predicate is set back to its original value.

- If rotating registers [64, 9] are absent, the kernel (i.e., the new loop body after modulo scheduling has been performed) is unrolled to enable modulo variable expansion [42].

- The appropriate prologue and epilogue code sequences are generated depending on whether this is a DO-loop, WHILE-loop or a loop with early exits, and on whether predicated execution and rotating registers are present in the hardware [63]. If there are early exit branches in the body of the loop, the corresponding epilogues must be crafted appropriately [43]. The schedule for the kernel may be adapted for the prologue and epilogues. Alternatively, the prologue and epilogues can be scheduled along with the rest of the code surrounding the loop while honoring the constraints imposed by the schedule for the kernel.

- Rotating register allocation [62] (or traditional register allocation if modulo variable expansion was done) is performed for the kernel. The prologue and epilogues are treated along with the rest of the code surrounding the loop in such a way as to honor the constraints imposed by the register allocation for the kernel.

- Finally, if the hardware has no predicated execution capability [64, 40, 9], reverse IF-conversion [77] is employed to regenerate control flow.

Ideally, the processor provides architectural support in the form of predicated execution, suppression of spurious exceptions due to speculative execution, rotating registers and special branch opcodes. These and other capabilities useful for achieving high levels of ILP have been gathered together in HPL PlayDoh, an architecture designed to facilitate research in ILP [40].

The subject of this report is the modulo scheduling algorithm itself, which is at the heart of this entire process. This includes the computation of the lower bound on the initiation interval. The reader is referred to the papers cited above for a discussion of the other steps that either precede or follow the actual scheduling.

¥

Although the modulo scheduling framework was formulated over a decade ago [61], at least two product compilers have incorporated modulo scheduling algorithms [57, 20], and any number of research papers have been written on this topic [34, 42, 70, 75, 76, 36], there exists a vague and unfounded perception that modulo scheduling is computationally expensive, too complicated to implement, and that the resulting schedules are sub-optimal.

In large part, this is due to the fact that there has been little work done either to thoroughly evaluate individual algorithms and heuristics for modulo scheduling, or to compare competing alternatives, from the viewpoints of schedule quality and computational complexity. The IMPACT group at the University of Illinois [11, 76] has compared Cydrome's approach to modulo scheduling [20] with the GURPR\* algorithm [68] and with hierarchical scheduling [42]. Allan and her co-workers [4] have compared iterative modulo scheduling, as described in this report and previously [60], with the Petri Net approach to the unroll-while-schedule strategy [56].

This report makes a contribution in this direction by describing a practical modulo scheduling algorithm which is capable of dealing with realistic machine models. Also, it reports on a detailed evaluation of the quality of the schedules generated and the computational complexity of the scheduling process. For lack of space, this report does not attempt to provide a comparison of the algorithm described here to other alternative approaches for software pipelining. Also, the goal of this report is not to justify software pipelining. The benefits of this, just as with any other compiler optimization or transformation, are highly dependent upon the workload that is of interest. Each compiler writer must make his or her own appraisal of the value of this capability in the context of the expected workload.

The remainder of this report is organized as follows. Section 2 provides an introduction to the modulo scheduling framework. Section 3 discusses the algorithms used to compute the lower bound on the initiation interval. Section 4 describes the iterative modulo scheduling algorithm in detail. Section 5 presents experimental data on the quality of the modulo schedules and on the computational complexity of the algorithms used. Section 6 discusses other algorithms for modulo scheduling and Section 7 states the conclusions.

**,**

# 2 Modulo scheduling

ŧ

### 2.1 The dependence graph

In general, each operation in the body of the loop is dependent upon one or more operations. These dependences may either be data dependences (flow, anti- or output) or control dependences [29, 78]. The dependences can be represented as a graph, with each operation represented by a vertex in the graph and each dependence represented by a directed edge to an operation from the operation upon which it is dependent. There may be multiple edges, possibly with opposite directions, between the same pair of vertices.

| Type of dependence | Delay                                     | Conservative<br>Delay |

|--------------------|-------------------------------------------|-----------------------|

| Flow dependence    | Latency(predecessor)                      | Latency(predecessor)  |

| Anti-dependence    | 1-Latency(successor)                      | 0                     |

| Output dependence  | 1+Latency(predecessor)-Latency(successor) | Latency(predecessor)  |

Table 1: Formulae for calculating the delays on data dependence edges.

Each edge possesses an attribute, which is the **delay**, i.e., the minimum time interval that must exist between the start of the predecessor operation and the start of the successor operation. In general, this is influenced by the type of the dependence edge and the execution latencies of the two operations as specified in Table 1. For an archetypal VLIW processor with non-unit architectural latencies, the delay for an anti-dependence or output dependence can be negative if the latency of the successor is sufficiently large. This is because it is only necessary that the predecessor start at the same time as or finish before, respectively, the successor finishes. A more conservative formula for the computation of the delay, which assumes only that the latency of the successor is not less than 1, is also shown in Table 1. This is more appropriate for superscalar processors.

A loop contains a recurrence if an operation in one iteration of the loop has a direct or indirect dependence upon the same operation from a previous iteration. Clearly, in the chain of dependences between the two instances of the operation, one or more dependences must be between operations that are in different iterations. We shall refer to such dependences as interiteration dependences<sup>1</sup>. Dependences between operations in the same iteration are termed intra-iteration dependences. A single notation can be used to represent both types of dependences. The distance of a dependence is the number of iterations separating the two operations involved. A dependence with a distance of 0 connects operations in the same iteration, a dependence from an operation in one iteration to an operation in the next one has a distance of 1, and so on. The dependence distance is specified as a second attribute on the edge.

The existence of a recurrence manifests itself as a circuit in the dependence graph. The sum of the distances around the circuit must be strictly positive. A **strongly connected component** (SCC) of the dependence graph is a maximal set of vertices and the edges between them such that within this sub-graph a path exists from every vertex to every other vertex. Since every operation on a recurrence circuit is reachable from any other operation on that circuit, they must necessarily all be part of the same SCC.

## 2.2 The modulo scheduling framework

If we knew the exact trip count, i.e., the actual number of iterations of the loop when executed, we could achieve close to the best possible performance by unrolling the loop completely, treating the resulting code as a single basic block and generating the best possible schedule. This is not a practical strategy since we do not generally know the trip count at compile-time and, even if we did, this completely unrolled code would usually be unacceptably large<sup>2</sup>. Instead, imagine the following *conceptual* strategy. First, we unroll the loop completely. Then we schedule the code but with two constraints:

- all iterations have identical schedules, except that

- each iteration is scheduled to start some fixed number of cycles later than the previous iteration.

Assume that a legal schedule is obtained, somehow, that meets the above two constraints. The fixed delay between the start of successive iterations is termed the **initiation interval (II)**. (We

.\*

<sup>&</sup>lt;sup>1</sup> Such dependences are often referred to as loop-carried dependences.

$<sup>^2</sup>$  However, if the trip count is a small compile-time constant, as often is the case, for instance, in graphics applications, complete unrolling of the loop can be a worthwhile strategy.

shall return to the questions of how the II and the schedule are actually determined.) Because of the constraints above, the schedule for the unrolled code is repetitive except for a portion at the beginning and a portion at the end.

This repetitive portion can be re-rolled to yield a new loop which is termed the **kernel**. The **prologue** is the code that precedes the repetitive part and the **epilogue** is the code following the repetitive part. By executing the prologue, then the kernel an appropriate number of times, and finally the epilogue, one would come close to re-creating the ideal, unconstrained schedule for the unrolled code. If this strategy is successful, a relatively small amount of code would be able to approximate the ideal (but impractical) strategy of unrolling the loop completely and scheduling it.

This approach to scheduling loops is modulo scheduling. The objective of modulo scheduling is to engineer a schedule for one iteration<sup>1</sup> of the loop such that when this same schedule is repeated at intervals of II cycles, no intra- or inter-iteration dependence is violated, and no resource usage conflict arises between operations of either the same or distinct iterations. Since instances of the same operation from successive iterations are scheduled II cycles apart, legality of the schedule from a resource usage viewpoint is preserved by ensuring that, within a single iteration, no machine resource is used at two points in time that are separated by an interval which is a multiple of the II. In other words, within the schedule for a single iteration, the same resource is never used more than once at the same time modulo the II. We shall refer to this as the **modulo constraint** and it is from this constraint that the name modulo scheduling is derived. It is also the objective of modulo scheduling to generate a schedule having the smallest possible II, since this is the primary determinant of performance except in the case of very short trip counts.

#### 2.3 Deducing the implied code motion from the modulo schedule

Let us consider more carefully how exactly the repetitive schedule is re-rolled conceptually and how the structure of the modulo scheduled code is determined. The schedule for a single iteration of the loop can be divided into **stages** consisting of II cycles each. The number of stages in one iteration is termed the **stage count** (SC). Likewise, the schedule for the conceptually unrolled loop, constrained in the manner described above, can also be divided into stages of II cycles. During each of the first SC-1 stages, a new iteration of the loop begins without the first one having

$<sup>^{1}</sup>$  As noted previously, due to pre-unrolling, a single iteration at this point may correspond to multiple iterations of the original loop.

as yet ended. From the SC-th stage on, one iteration completes for every one that starts until the last iteration has started. This is the repetitive part of the schedule which will be re-rolled into the kernel. Every iteration of the kernel performs one stage each (and a different one if SC > 1) from SC consecutive iterations of the original loop.

The schedule for the kernel is obtained from that for a single iteration of the loop by superimposing the schedules for each stage of the latter, i.e., by wrapping around the schedule for one iteration of the loop, modulo the II. Thus, the schedule for the kernel is exactly II cycles long. In the VLIW case, the code for the kernel will also be exactly II instructions long. Each VLIW instruction contains all of the operations that are scheduled in a single cycle of the kernel schedule. Note that these operations will, in general, come from different iterations of the loop.

The last cycle of the kernel coincides with the last cycle of each stage--one stage each from SC consecutive iterations. Assuming that the loop-closing branch has an n cycle latency, the branch *must* be scheduled in the n-th last cycle of the stage in which it is scheduled. This constitutes a scheduling contraint upon the branch operation if the stage boundaries within an iteration have already been determined. Alternatively, the branch operation may be freely scheduled and the stage boundaries are then uniquely determined. We shall adopt the former approach. In the event that the II is less than n, the kernel has less than n instructions and it becomes impossible to place the branch in the n-th last instruction. In such cases, the kernel must be unrolled enough so that the unrolled kernel has at least n instructions. In all cases, the target of the branch operation is the first instruction of the kernel.

By looking at the modulo schedule for a single iteration, we can decide what code motion is implicit in the schedule that we have adopted. The operations in the stage containing the branch operation are the only ones that have not been moved around the back-edge. All operations in earlier (later) stages have been moved backwards (forwards) around the back-edge to a previous (subsequent) iteration. The greater the distance of a stage from the one containing the branch, the larger is the number of times that the operations have been moved around the back-edge. The number of stages before (after) the one with the branch is equal to the number of iterations that were conceptually peeled off at the end (beginning) of the loop to permit these code motions across the back-edge. With this understanding, the code for the prologue and the epilogue(s) can be determined.

ţ

Thus, from the modulo schedule we get not only the desired schedule for the kernel but also the requisite amount of iteration peeling and code motion. The important point to note is that the requisite inter-block code motions are implicit in, and are determined by, the schedule which, in turn, is engineered so as to directly optimize a relevant figure-of-merit such as the II. This is to be contrasted with a philosophy in which operations are moved across the back-edge using ad hoc heuristics, in the hope that the resulting schedule will be near-optimal.

A detailed discussion of how the prologue, kernel and epilogue are structured, with and without predicated execution, with and without rotating registers, for DO-loops as well as for WHILE-loops and loops with early exits is discussed by Rau, et al. [63]. If there are early exit branches in the body of the loop, there are further subtleties in how the corresponding epilogues are crafted [43].

# 2.4 The minimum initiation interval (MII)

ţ

Modulo scheduling requires that a candidate II-be selected before scheduling is attempted. A smaller II corresponds to a shorter execution time. The **minimum initiation interval (MII)** is a lower bound on the smallest possible value of II for which a modulo schedule exists. The candidate II is initially set equal to the MII and increased until a modulo schedule is obtained. The MII can be determined either by a critical resource that is fully utilized or a critical chain of dependences running through the loop iterations. The MII can be calculated by analyzing the computation graph for the loop body. One lower bound is derived from the resource usage requirements of the computation. This is termed the **resource-constrained MII (ResMII)**. The **recurrence-constrained MII (RecMII)** is derived from latency calculations around elementary circuits in the dependence graph for the loop body. The MII must be equal to or greater than both the ResMII and the RecMII. Thus

Any legal II must be equal to or greater than the MII. As we shall see, in the face of recurrences and/or complex patterns of resource usage, the MII is not necessarily an achievable lower bound. The calculation of the ResMII and RecMII bounds are detailed in Section 3.

# 2.5 Dynamic Single Assignment

\*

Anti- and output dependences can have an extremely detrimental effect upon the RecMII. In particular, every operation is anti-dependent, with a dependence distance of 1, upon all the operations that are flow dependent upon it. This is so since all of these flow dependent operations must be issued before their common source register is overwritten by the same operation from the next iteration. Together, these flow and anti-dependences can set up recurrence circuits in the data dependence graph which greatly increase the RecMII.

In acyclic (loop-free) code, one can eliminate anti-dependences via a program representation known as **static single assignment (SSA)** [29]. Very simply, this consists of never using the same virtual register as a destination more than once in the entire program. Since each virtual register has a result assigned to it exactly once, the problem of overwrites and the attendent antiand output dependences cannot occur. A problem arises in the case of cyclic control flow graphs. Even after putting the code into the SSA form, we cannot avoid the fact that each time flow of control revisits a particular operation, the same virtual register is assigned a new value. Consequently, this operation must be made anti-dependent upon all operations that use the previous value in the destination register.

We eliminate these anti-dependences by enhancing the concept of a virtual register. An **expanded virtual register (EVR)** is an infinite, linearly ordered set of virtual registers with a special operation, **remap()**, defined upon it [59]. The elements of an EVR, v, can be addressed, read, and written as v[n], where n is any integer. For convenience, v[0] may be referred to as merely v. The effect of remap(v) is that whatever EVR element was accessible as v[n] prior to the remap operation will be accessible as v[n+1] after the remap operation. Except for registers holding loop invariants, all registers are implicitly remapped when the loop-closing branch is taken. Although textually it might appear that register v is being assigned to repeatedly, dynamically it is still single assignment; a different element of the EVR is assigned to on each occasion.

A program representation is in the **dynamic single assignment (DSA)** form [59] if the same virtual register (EVR element) is never assigned to more than once on any dynamic execution path. The static code may have multiple operations with the same virtual destination register as long as these operations are in mutually exclusive basic blocks or separated by (implicit) remap operations. In this form, a program has no anti- or output dependences due to register usage but may possess such dependences due to loads and stores to the same, or potentially the same, memory location.

Of course, as with conventional virtual registers, EVRs are a fiction that cannot be translated into hardware. The infinite number of virtual registers in each EVR, of which there are an unlimited number, must be mapped into a finite number of physical registers. In fact, only a finite, contiguous set of the elements of an EVR may be expected to be live at any point in time, and only these need to be allocated physical registers. This register allocation step will re-introduce anti-dependences, but it must be done in such a manner as to never introduce an anti-dependence that contradicts the schedule just created.

The rotating register file [64] is one way of directly providing hardware support for the EVR concept. The remapping is implemented by providing a circular register file with a pointer into it that is decremented each time a new iteration is started. Addressing into the register file is relative to this pointer. However, EVRs are of value in the intermediate representation even when there are no rotating registers provided in the hardware. The use of EVRs makes it possible to temporarily ignore anti- and output dependences and thereby engineer an optimal or near-optimal modulo schedule. Thereafter, the anti- and output dependences can be honored, without compromising the schedule by unrolling the kernel an appropriate number of times and performing modulo variable expansion, i.e., virtual register renaming [42]. In effect, remapping is simulated by code replication and register renaming. Register allocation for modulo scheduled loops is discussed in greater detail by Rau, et al. [62].

Although dynamic single assignment is generally better, it is worth noting that there are situations in which dynamic multiple assignment is preferable despite the anti-dependences that are introduced. If DSA is rigidly adhered to, copy operations must be introduced at the site of every  $\phi$ function [29], one for each predecessor block at the point of a control flow merge. (Alternatively, when there are two predecessor basic blocks, a select operation may be used, and if there are more than two predecessor blocks, a tree of selects must be used.)

These copy operations can increase the schedule length if they are on the critical path or if they require the use of a critical resource. The copy operations can be eliminated by renaming the virtual registers on the input side of the  $\phi$ -function to be the same as the output. Often this will not introduce anti-dependences since the multiple static assignments are mutually exclusive. In those cases where an anti-dependence is introduced, its effect on the schedule length can either be better or worse than the effect of the copy operations. It is currently not well understood how this choice should be made.

ł

The important point, however, is that EVRs make it possible to retain only those anti-dependences that are desirable from the viewpoint of schedule length. In the absence of EVRs, the loop may be unrolled and put into the static single assignment form. If the loop is unrolled adequately, the loop-carried anti-dependences will not degrade the schedule. Unfortunately, the extent of unrolling required is known precisely only *after* modulo scheduling is performed, whereas the unrolling, if performed, must be done *before* modulo scheduling.

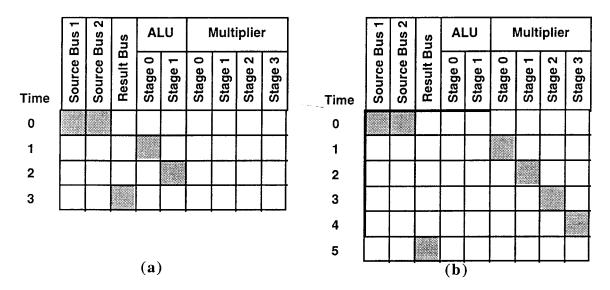

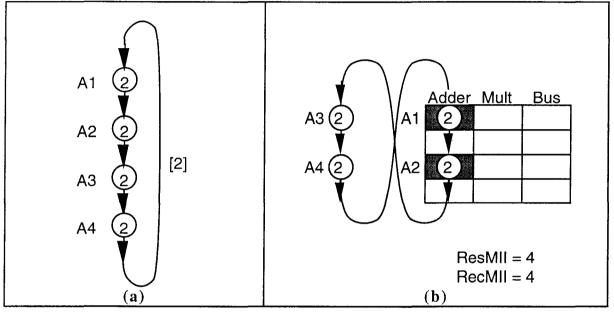

### 2.6 Modelling and tracking resource usage

The resource usage of a particular opcode is specified as a list of the resources used by the operation, and the times at which each of those resources is used relative to the time of issue of the operation. For this purpose, we shall consider resources that are at the level of a pipeline stage of a functional unit, a bus or a field in the instruction format. Figure 1a is a pictorial representation of the resource usage behavior of a highly pipelined ALU operation, with an execution latency of four cycles, which uses the two source operand buses on the cycle of issue, uses the two pipeline stages of the ALU on the next two cycles, respectively, and then uses the result bus on its last cycle of execution. Likewise, Figure 1b shows the resource usage behavior of a multiply operation on the multplier pipeline. This method of modelling resource usage is termed a **reservation table** [15].

A particular operation (opcode) may be executable in multiple ways, with a different reservation table corresponding to each one of these ways. In this case, the operation is said to have multiple **alternatives**. Frequently, but not always, each alternative corresponds to the use of one of the multiple functional units on which this operation can be executed. In general, these functional units might not be equivalent. For instance, a floating-point multiply might be executable on two functional units, of which only one is capable of executing divide operations.

When performing scheduling with a realistic machine model, a data structure similar to the reservation table is employed to record that a particular resource is in use by a particular operation at a given time. We shall refer to this as the **schedule reservation table** to distinguish it from those for the individual operations. When an operation is scheduled, its resource usage is recorded by translating, in time, its own reservation table by an amount equal to the time at which it is scheduled, and then overlaying it on the schedule reservation table [72]. Scheduling it at that time is legal only if the translated reservation table does not attempt to reserve any resource at a time

when it is already reserved in the schedule reservation table. When backtracking, an operation may be "unscheduled" by reversing this process.

The nature of the reservation tables for the opcode repertoire of a machine determine the complexity both of computing the ResMII and of scheduling the loop. A **simple reservation table** is one which uses a single resource for a single cycle on the cycle of issue (time 0). A **block reservation table** uses a single resource for multiple, consecutive cycles starting with the cycle of issue. Any other type of reservation table is termed a **complex reservation table**. Block and complex reservation tables cause increasing levels of difficulty for the scheduler. Both reservation tables in Figure 1 are complex.

Figure 1. Reservation tables for (a) a pipelined add, and (b) a pipelined multiply.

From Figure 1, it is evident that an ALU operation (such as an add) and a multiply cannot be scheduled for issue at the same time since they will collide in their usage of the source buses. Furthermore, although a multiply may be issued any number of cycles after an add, an add may not be issued two cycles after a multiply since this will result in a collision on the result bus. The set of forbidden intervals, due to resource conflicts, between the initiation of two operations with the same reservation table can be collected together into what is termed the **collision vector** for that reservation table [15]. Likewise, the set of forbidden intervals, due to resource conflicts, between

1

the initiation of an operation with one reservation table and a second operation with another reservation table is termed the **cross-collision vector** for that pair of reservation tables.

Given the set of reservation tables for a particular machine, one can compute the complete set of collision and cross-collision vectors. In general, their are many sets of reservation tables that yield the same set of collision and cross-collision vectors. Some of these sets are smaller and simpler than others. It is possible to compute a synthetic set of reservations tables that are preferable to the original set [26]. For instance, in Figure 1, if the ALU and multiplier possessed their own, separate source and result buses and if all operations that used these two pipelines used precisely the same reservation tables, then both reservation tables could be replaced by simple reservation tables.

## 2.7 A simplistic modulo scheduling algorithm

Having eliminated all undesirable anti- and output dependences due to register usage and having computed the MII, the next step is to generate a modulo schedule. In the simplest case, a minor modification [61] of the commonly used, greedy, list scheduling<sup>1</sup> algorithm [1, 41] serves the purpose. The only change is that an operation P may not be scheduled at a time t such that if P were scheduled at time t±k\*II for any  $k \ge 0$ , it would have a resource conflict with a previously scheduled operation (from the same iteration). Normally in list scheduling, only the case k = 0 is considered.

An acyclic scheduler keeps track of resource usage by means of the schedule reservation table, which may be conceptualized as a table in which each column corresponds to a particular resource, and each row corresponds one cycle. If scheduling an operation at some particular time involves the use of resource R at time T, then entry [T,R] of the schedule reservation table is used to record that fact. In the case of modulo scheduling, adherence to the modulo constraint is facilitated by the use of a special version of the schedule reservation table [61]. If scheduling an operation at some particular time involves the use of resource R at time T, then entry [(T mod II),R] of the schedule reservation table is used to record it. Consequently, the schedule reservation table need only be as long as the II. Such a reservation table has been aptly dubbed a **modulo reservation table** (**MRT**) by Lam [42].

ţ

<sup>&</sup>lt;sup>1</sup> List scheduling refers to the class of scheduling algorithms in which all of the operations are ordered into a list, once and for all, based on some priority function, and are then scheduled in the order specified by that list.

This minor variant of the list scheduling algorithm is, in fact, guaranteed to yield a legitimate schedule with an II equal to MII if the loop is such that the only recurrence circuits are trivial ones involving a single operation and if the machine is such that every operation has simple reservation tables. When either assumption is invalid, this scheduling algorithm can fail to find a schedule for an II that is equal to the MII.

# 2.8 Complicating factors in modulo scheduling

The existence of recurrences and complex reservation tables can, individually or jointly, result in the non-existence of a valid schedule at the MII. Furthermore, because of these two factors, a greedy, one-pass scheduling algorithm, such as list scheduling, cannot guarantee that it will find a modulo schedule for a given II, even when such a schedule exists.

#### 2.8.1 Difficulty in finding a schedule for a feasible initiation interval

The new phenomenon that recurrences introduce to the scheduling process is that of a deadline, i.e., the requirement that an operation be scheduled *no later than* some particular time. When the first operation in a SCC is scheduled, it imposes constraints on how late all of its predecessor operations can finish and, therefore, on how late they can start. Since this operation is in a SCC, the rest of the operations in the SCC are its predecessors as well as its successors. These successors are, as yet, unscheduled (since the operation under consideration was the first one in the SCC to be scheduled) and all of them now have deadlines on the latest time by which they must be scheduled. From then on, the scheduling algorithm must be sensitive to these deadlines. If any one of these deadlines cannot be honored, the partial schedule generated thus far represents a dead end that cannot lead to a valid schedule.

In particular, if the first operation that is scheduled from a SCC is scheduled greedily, at the earliest possible time, the deadlines may be more constraining than they need have been, and a legal schedule may not be found. In such a case, it would have been preferable to have scheduled that operation somewhat later than the earliest possible time. Yet, as a rule, it is preferable to schedule operations as early as possible, in order to minimize the schedule length. This represents a dilemma for a greedy, one-pass scheduler.

2

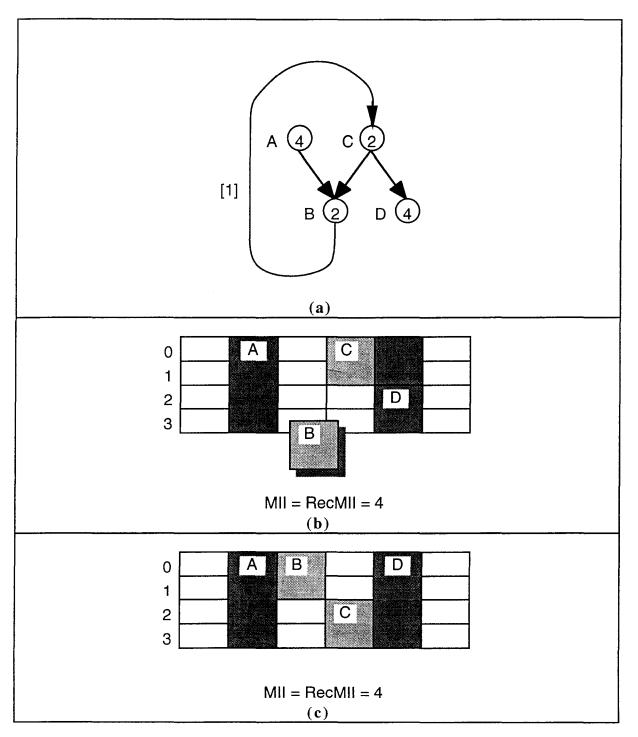

Figure 2. An example demonstrating the problem with greedy scheduling in the presence of recurrences. (a) The data dependence graph. (b) The resulting partial schedule when C is scheduled greedily. B cannot be scheduled. (c) The resulting valid schedule when C is scheduled two cycles later.

ł

If list scheduling is employed and one gets into a situation wherein an operation cannot be scheduled by its deadline, scheduling cannot proceed any further; any resulting schedule is guaranteed to be invalid. In general, only an exhaustive, back-tracking search over the space of possible schedules is guaranteed to yield a valid schedule for the candidate II, if one in fact exists.

Consider the loop in Figure 2a. In this and the following examples, the label next to each vertex is its name, and the latency of each operation is indicated within the vertex. The delay on each edge is understood to be the latency of the source vertex, and the distance of each edge is understood to be zero unless it is explicitly shown in brackets. If list scheduling is employed on this example, the partial schedule in Figure 2b is obtained. The operation B cannot be scheduled since the earliest time at which it can be scheduled is 4 which is greater than the deadline imposed upon it by the fact that its successor operation C (from the next iteration) is scheduled at time 4 (4 cycles later than the latest by cycle 2 and this is impossible since A only finishes at the end of cycle 3.

The problem in this case is that operation C was scheduled at the earliest possible time, which generally is a good policy. In this case, if it had been scheduled 2 cycles later, at time 2, the deadline for operation B would have been extended to time 4 which would have made it possible to arrive at the valid schedule in Figure 2c. An exhaustive search would have yielded this schedule sooner or later. However, the computational complexity of such a process is exponential in the number of operations and, for all but the smallest loops, is not a practical approach.

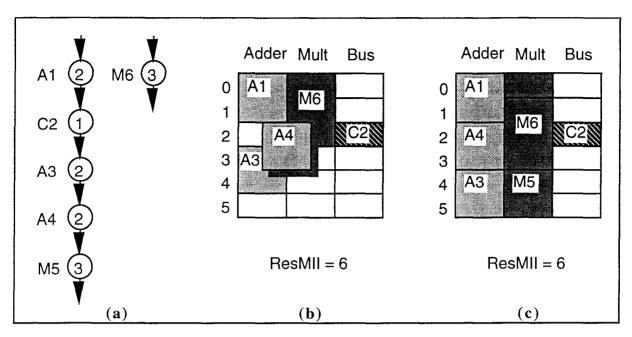

Greedy scheduling can also lead to a dead-end as a result of the interaction of block or complex reservation tables. The example in Figure 3a consists of a chain of operations, A1 through M5, and one independent operation, M6. A1, A3 and A4 are non-pipelined adds that take two cycles each on the adder, M5 and M6 are non-pipelined multiply operations that take three cycles each on the multiplier, and C2 is a copy operation that uses the bus for one cycle.

The typical list scheduling algorithm would result in A1, M6, C2, and A3 being scheduled in that order yielding a partial schedule and an MRT state as shown in Figure 3b. A4 cannot be scheduled because the only free adder slots, at times 2 and 5 modulo 6, are not contiguous as required by the block reservation table for A4. If, however, A3 had been scheduled one cycle later that the earliest possible time, at time 4 as in Figure 3c, an acceptable schedule is obtained.

ţ

Figure 3. An example demonstrating the problem with greedy scheduling in the presence of block or complex reservation tables. (a) The data dependence graph. (b) The resulting partial schedule when A1, M6, C2, and A3 are scheduled greedily. A4 cannot be scheduled. (c) The resulting valid schedule when A3 is scheduled one cycle later.

These are problems that acyclic list scheduling does not have to cope with. As these examples demonstrate, a simple, modulo-constrained version of greedy list scheduling is inadequate. Although greedy scheduling is generally a good idea in order to minimize the schedule length, it can also lead to a partial schedule which is a dead end. Some form of backtracking is required, which yields a final schedule in which the appropriate operations have been scheduled in a non-greedy fashion. The specific form of backtracking adopted is discussed in Section 4.

#### 2.8.2 Infeasibility of the minimum initiation interval

ł

In the presence of block or complex reservation tables, or due to the existence of recurrence cycles, it can be the case that there is no valid schedule possible at the computed MII.

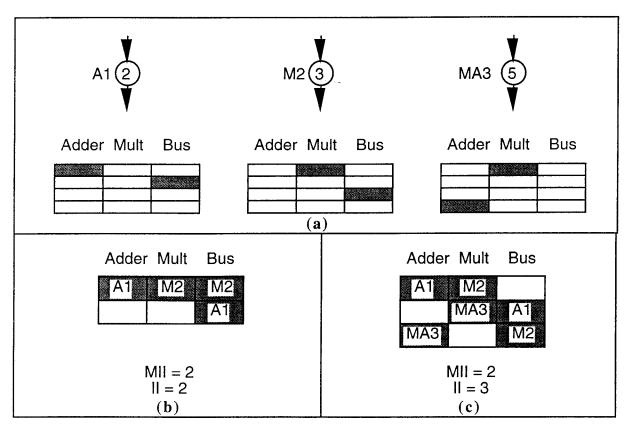

Consider the example of a loop consisting of the three independent operations shown in Figure 4a and their respective complex reservation tables. Between the three operations, each resource is used exactly twice, yielding a ResMII of 2. Figure 4b shows the MRT for an II of 2. After A1 and M2 have been scheduled, it is impossible to schedule MA3. A little reflection shows that the three

reservation tables are, in fact, incompatible for an II of 2, but are compatible for an II of 3 (Figure 4c).

A second example shows why a valid schedule may turn out to be impossible for II = MII, even in the absence of block or complex reservation tables, as a consequence of the contradictory constraints of the recurrence dependences and the (simple) reservation tables. Consider the loop (Figure 5a) consisting of four fully pipelined add operations, A1 through A4, each one dependent upon the previous one with a dependence distance of 0, and with A1 dependent upon A4 with a distance of 2. Assuming that the add latency is 2, this yields a RecMII of 4. Also, assuming each add uses each stage of the single pipelined adder for one cycle, the ResMII is equal to 4. Thus, the MII is 4.

Figure 4. An example demonstrating the infeasibility of the MII in the presence of complex reservation tables. (a) The three operations and their reservation tables. (b) The MRT corresponding to the dead-end partial schedule for an II of 2 after A1 and M2 have been scheduled. (c) The MRT corresponding to a valid schedule for an II of 3.

•

However, a schedule cannot be obtained for II = MII = 4 (Figure 5b). As soon as A1 is scheduled at time 0, the latest start times for A2 through A4 are 2, 4 and 6, respectively, based on the latency of the add operation. These are also the earliest start times for those operations and, so, based on the dependence constraints, A2, A3 and A4 must be scheduled at cycles 2, 4 and 6, respectively. Unfortunately, 4 and 6 are equal to 0 and 2, respectively, modulo the II of 4, which means that A3 and A4 have resource conflicts with A1 and A2, respectively. The only schedule from a dependence viewpoint is unacceptable from a resource usage viewpoint. No valid schedule exists for II = 4.

Figure 5. An example demonstrating the infeasibility of the MII due to the interaction between the recurrence constraints and the resource usage constraints. (a) The data dependence graph. (b) The MRT corresponding to the dead-end partial schedule for an II of 4 after A1 and A2 have been scheduled.

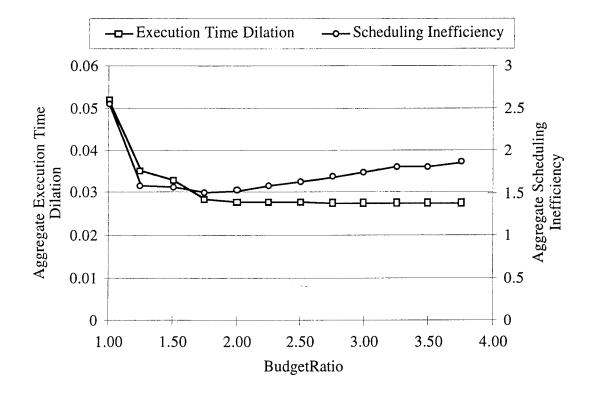

In such cases, an exhaustive search will eventually reveal the absence of a valid schedule by coming up empty-handed. However, the exponential amount of computational effort needed to discover this fact, is unacceptable. A reasonable strategy is to give up on a candidate II after expending a pre-allocated budget of time, and to try again at a larger value of II.

ł

# **3** Calculation of the minimum initiation interval (MII)

The minimum initiation interval, MII, is the larger of the resource-constrained MII, ResMII, and the recurrence-constrained MII, RecMII. In general, it will be some non-integer, f. However, modulo scheduling requires an integer-valued II. If f is not an integer, and if the loop is not to be unrolled, an integer-valued MII is obtained by rounding the f up to the next larger integer. Alternatively, if the loop is to be pre-unrolled with an unroll factor of U, as discussed in Section 1, the corresponding MII is  $[f^*U]$ . We now address the method by which the ResMII and the RecMII are computed.

## 3.1 The resource-constrained MII (ResMII)

The resource-constrained lower bound on the II, ResMII, is calculated by totaling, for each resource, the usage requirements imposed by one iteration of the loop. The exact ResMII can be computed by performing an optimal bin-packing of the reservation tables for all the operations, a computation that is of exponential complexity. Complex reservation tables and multiple alternatives make it worse yet and it is impractical, in general, to compute the ResMII exactly. Instead, an approximation to this exact lower bound is computed.

The ResMII is computed by first sorting the operations in the loop body in increasing order of the number of alternatives, i.e., degrees of freedom, and initializing the usage count of each resource to zero. At each step in the algorithm, the partial ResMII is defined to be the usage count of the most heavily used resource at that point. The operations are processed in sort order. For an operation with multiple alternatives, each alternative is selected in turn. The number of times it uses each resource is added to the current usage count for that resource in order to determine the partial ResMII that would result if this alternative were actually used. For each operation, that alternative is selected which yields the lowest partial ResMII. When all operations have been considered, the usage count for the most heavily used resource constitutes the ResMII. It is important to note that this selection between the alternatives is only for the purpose of computing the ResMII. During scheduling, the scheduler has complete freedom to select the alternative that will actually be used.

The method above yields an integer-valued ResMII. In general, the ResMII is a real-valued number and ought to be computed as such. For instance, if the floating-point adders are the most heavily used functional units, there are three of them and there are 8 add operations, the ResMII is 8/3. More generally, if the functional units can be partitioned into equivalence classes, such that all of

ž

the functional units in a given equivalence class can perform exactly the same set of operations, and if the operations are such that each one can be performed by precisely one equivalence class, then the ResMII can be computed by taking ratio of the number of operations to be executed on a given equivalence class and dividing that number by the number of functional units in that equivalence class. The largest such ratio, across all of the equivalence classes, is the ResMII.

Unfortunately, many real machines do not possess any such structure, and there exists no good technique for computing the real-valued ResMII. One approximate way to do so is to *conceptually* unroll the loop U times, calculate the integer-valued ResMII for this unrolled loop, and then divide that by U.

## 3.2 The recurrence-constrained MII (RecMII)

The RecMII is calculated using the dependence graph discussed in Section 2.1. All undesirable anti- and output dependences are assumed to have been eliminated, in a preceeding step, by the use of expanded virtual registers (EVRs) and dynamic single assignment as discussed in Section 2.5.

A loop contains a recurrence if an operation in one iteration of the loop has a direct or indirect dependence upon the same operation from a previous iteration. The existence of a recurrence manifests itself as a circuit in the dependence graph. Assume that the sum of the delays along some elementary circuit<sup>1</sup> c in the graph is Delay(c) and that the sum of the distances along that circuit is Distance(c). The existence of such a circuit imposes the constraint that the scheduled time interval between an operation on this circuit and the same operation Distance(c) iterations later must be at least Delay(c). However, since the schedule for each iteration is the same as that for the previous iteration, except that it is delayed by II cycles, this time interval is Distance(c)\*II. Consequently, we have the constraint that

$$Delay(c) - II*Distance(c) \le 0.$$

This is the constraint upon the II imposed by this one recurrence circuit. The RecMII is determined by considering the worst-case constraint across all circuits. One approach is to enumerate in an irredundant fashion all the elementary circuits in the graph [69, 49], calculate the smallest value of

Ż

<sup>&</sup>lt;sup>1</sup> An elementary circuit in a graph is a path through the graph which starts and ends at the same vertex (operation) and which does not visit any vertex on the circuit more than once.

II that satisfies the above inequality for each individual circuit, and to use the largest such value across all circuits. Thus,

$$\operatorname{RecMII} = \operatorname{Max}_{c \in C} \left( \frac{\operatorname{Delay}(c)}{\operatorname{Distance}(c)} \right).$$

Along with a few additional optimizations, this is the approach used in Cydrome's compiler for the Cydra 5 [20].

A second approach is to pose the task of computing the RecMII as a linear programming problem [16, 17] where the objective function to be minimized is the II and the constraints are that for each pair of operations, P and S, that are connected by an edge from P to S, the following inequality be satisfied:

$$T(S) + II*Distance(P,S) - T(P) \ge Delay(P,S)$$

where  $T(\bullet)$  is the time at which the operation is scheduled.

ł

The third approach, the one used in this study, is to pose the problem as a minimal cost-to-time ratio cycle problem [44] as proposed by Huff [36]. A version of this algorithm, which can be used to compute the RecMII, as well as for other purposes, is shown in Figure 6.

The algorithm ComputeMinDist computes, for a given II, the MinDist matrix whose [i,j] entry specifies the minimum permissible interval between the time at which operation i is scheduled and the time at which operation j, *from the same iteration*, is scheduled. If there is no path from i to j in the dependence graph, the value of the entry is  $-\infty$ . If MinDist[i,i] is positive for any i, it means that i must be scheduled later than itself, which is clearly impossible. This indicates that the II is too small and must be increased until no diagonal entry is positive. On the other hand, if all the diagonal entries are negative, it indicates that there is slack around every recurrence circuit and that the II is larger than it need be. Since we are interested in finding the minimum legal II, at least one of the diagonal entries should be equal to 0. The smallest value of II, for which no diagonal entry is positive and at least one is zero, is the RecMII. In general, the RecMII computed in this way will not be an integer. If this is the case, and if only an integer-valued RecMII is of interest, the next larger integer is selected at the RecMII. In this case, no entry along the diagonal of the MinDist matrix will be 0.

```

function ComputeMinDist (II: integer; NumberOfOperations: integer): boolean;

{ Compute the longest path between every pair of vertices.

{

Return TRUE if there is a positive cycle.

{

}

This function is repeatedly invoked to compute the RecMII }

{

as part of a binary search for the smallest value of II

}

{

for which there is no positive cycle.

}

label

1;

var

i, j, k: integer;

dist: integer;

PositiveCycle: boolean;

begin

{ Initialize the distance matrix with the adjusted delay

{ between pairs of operations that have an arc between them.}

for i := 1 to NumberOfOperations do

for j := 1 to NumberOfOperations do

MinDist[i, j] := -\infty;

for each edge e that goes from i to j do

MinDist[i, j] := Max(MinDist[i, j], (Delay[e] - II * Distance[e]));

PositiveCycle := false;

for k := 1 to NumberOfOperations do

{ Now consider all paths via vertex k as well }

for i := 1 to NumberOfOperations do

for j := 1 to NumberOfOperations do

dist := MinDist[i, k] + MinDist[k, j];

if dist > MinDist[i, j] then

MinDist[i, j] := dist;

if (i = j) and (dist > 0) then

PositiveCycle := true;

goto 1;

1:

ComputeMinDist := PositiveCycle;

end; { ComputeMinDist }

```

Figure 6. ComputeMinDist: an algorithm for computing the minimum permissible time interval between every pair of operations.

ComputeMinDist begins by initializing MinDist[i,j] with the minimum permissible time interval between i and j considering only the edges from i to j. If there is no such edge, MinDist[i,j] is initialized to  $-\infty$ . If e is an edge from i to j and if Distance(e) is zero, then edge e specifies that MinDist[i,j] be at least Distance(e). If, however, Distance(e) = d > 0, then the interval between the

operation i from one iteration and the operation j from d iterations later must be at least Distance(e). Since the operation j from the same iteration as i is scheduled d\*II cycles earlier, MinDist[i,j] must be at least as large as Distance(e) - d\*II. Once MinDist has been initialized, the minimal cost-to-time ratio cycle algorithm is used to compute MinDist for that candidate II. If MinDist has a positive entry along the diagonal, the candidate II is smaller than the RecMII. If all diagonal entries are greater than zero, the candidate II is greater than the RecMII. Thus, by repeatedly invoking ComputeMinDist, we can determine the RecMII.

Since the algorithm ComputeMinDist is  $O(N^3)$  and expensive for large values of N, the number of operations in the loop, it is desirable that it be invoked as few times as possible. If one is interested only in the MII, and not the RecMII, the initial trial value of II is the ResMII. If this yields no positive diagonal entry in the MinDist matrix, then it is the MII. Otherwise, the candidate MII is incremented until there are no positive entries on the diagonal. The value of the increment, which is initially 1, is doubled each time the MII is incremented. The candidate MII at this point is greater than or equal to the RecMII. A binary search is performed between this last, successful candidate MII and the previous unsuccessful value until the RecMII is found to the desired degree of floating-point precision. If only the integer MII is required, we start with the integer ResMII and only examine integer values for MII during the above binary search. (To compute the RecMII, the only difference is that the first candidate value tested is 1 and the last unsuccessful value tested is 0.) The number of times ComputeMinDist must be invoked for this strategy can be shown to be

$$\begin{cases} 1, & \text{if RecMII} \leq \text{ResMII}, \\ 2 * \lceil \log_2(1 + \text{RecMII} - \text{ResMII}) \rceil + F, & \text{otherwise.} \end{cases}$$

where F is the number of bits of fractional precision desired.

ļ

The statistics presented in Section 5 on the number of operations in a loop show that N can be quite large and, so,  $O(N^3)$  complexity is a matter of some concern. This problem can be addressed by considering small subsets of the overall dependence graph when computing the RecMII. Since every operation on a recurrence circuit is reachable from any other operation on that circuit, they must all be part of the same SCC. The important observation is that the RecMII can be computed as the largest of the RecMII values for each individual SCC in the graph. As the statistics in Section 5 demonstrate, there are very few SCCs that are large, and  $O(N^3)$  is quite a bit more tolerable for the small values of N encountered when N is the number of operations in a single SCC.

The same algorithm, ComputeMinDist can be used. The only difference is that it is fed the dependence graph for one SCC at a time rather than that for the entire loop. Each time ComputeMinDist is invoked with a new SCC, the initial starting value of the candidate MII is the resulting MII as computed with the previous SCC. For the first SCC, the initial value of MII is the ResMII.

# 4 Iterative modulo scheduling

÷

Since a one-pass scheduling algorithm will often not yield a valid schedule, and since an exhaustive search is generally unacceptable, the only option is to use some form of non-exhaustive search through the space of schedules. Each state in this search space corresponds either to a complete schedule, in which every operation has been scheduled, or a partial schedule, in which only some of the operations have been scheduled. Starting from a state in which no operation is scheduled, the goal is to find a complete schedule that is either optimal or near-optimal.

Search strategies can be categorized by whether or not they are deterministic, goal-directed searches. Examples of algorithms, that search through the search space in a semi-random fashion, are simulated annealing, the Boltzmann machine algorithm and genetic algorithms [65] and these have been applied to the modulo scheduling problem [38, 8, 19]. Such algorithms do not run the risk of getting trapped in a local minimum but, in the context of a production compiler, take an unacceptably long time to find a near-optimal solution. In contrast, goal-directed search algorithms are guided by heuristics in a deterministic fashion through the search space towards, what one hopes, is a global optimum. Although good heuristics improve the probability that the optimum found is the global optimum, the possibility exists, nevertheless, that the optimum may well be only a local one.

One approach, guaranteed to find an optimal solution, is to pose the task of finding a modulo schedule as an integer linear programming problem [28, 6, 25]. Although linear programming has exponential complexity in the worst-case, this is generally not the case in practice. Even so, the execution time of integer linear programming algorithms is far too great for them to be seriously considered for use in production compilers. On the other hand, this approach is useful for evaluating the quality of heuristics-based scheduling algorithms.

In the case of modulo scheduling, the problem of finding a local optimum is not an important one. To a first order, any legal schedule that is found for the desired II, is as good as any other. The bigger problem is that of finding oneself in a state, corresponding to a partial schedule, from which no forward progress is possible, i.e., no additional operation can be scheduled without violating some dependence or resource constraint. Goal-directed searches must have a strategy to deal with this situation.

One option is to backtrack some distance along the path in the search space that was taken to this dead-end and to then move forward again, branching off along a different path this time. Unless an exhaustive search is being performed, additional heuristics must be employed to determine how far to backtrack and which (different) path to take this time around. The task of selecting a better path to take from a given state on a subsequent attempt differs from the corresponding task on the first attempt in that one has knowledge of some number of failed attempts. Somehow, some information gathered from these failed attempts must guide the heuristic that selects a different path. Unfortunately, there are no known heuristics that are successful at exploiting such information. Indeed, it is not even understood what information is relevant to a better decision on a subsequent attempt.

Another option is to use a second heuristic to jump from the dead-end state corresponding to one partial schedule to some other state corresponding to another partial schedule. Thereafter, the first heuristic takes over once again in the search for a complete, feasible schedule. The hope is that a valid schedule will be found at the candidate II after searching only a small fraction of the entire space of schedules. Such a scheduling algorithm, if successful, would be more attractive than either a one-pass or an exhaustive-search algorithm. Of course, there is the possibility that such an algorithm, lacking the systematic search of the exhaustive algorithm, could either get locked into a repetitive orbit, circling around aimlessly through the space of partial schedules, never finding a valid one even though it has expended more effort than the exhaustive-search algorithm. It is crucial that good heuristics be employed to control both the search for a valid schedule and the choice of a next state when the search arrives at a dead-end. The iterative modulo scheduling algorithm, described in this report, is of this type.

It employs a deterministic, goal-directed search for a legal schedule at the candidate II. This bears a strong resemblance to the well-known list scheduling algorithm using height-based priorities. A second heuristic is used to jump from the dead-end state corresponding to one partial schedule to some other state corresponding to another partial schedule. When the scheduler finds that there is no available slot for scheduling the currently selected operation, it displaces one or more previously scheduled, conflicting operations. These are then, in turn, re-scheduled when the deterministic,

1

goal-directed search for a legal schedule continues. This behavior, of repeatedly scheduling and rescheduling operations, in search of a "fixed-point" solution which simultaneously satisfies all of the scheduling constraints, is why this algorithm for modulo scheduling is termed iterative.

If the search fails to yield a valid schedule even after a large number of steps, it is reasonable to assume that no feasible schedule exists at this II. The only option is to increase the candidate II by some amount and try again, in the belief that a schedule will be easier to find for a larger II. This seems reasonable from two viewpoints. First, a larger II results in a later deadline for every recurrence operation and, hence, more time slots in which that operation can be scheduled. In the extreme, once the II is equal to the schedule length of the (non-modulo) list schedule, even the one-pass list scheduling algorithm should work. Second, a larger II provides more usage time slots for every resource on the modulo reservation table, making it simpler to find a non-overlapping placement of the reservation tables for each operation.

# 4.1 An intuitive motivation for iterative modulo scheduling

Although a number of iterative algorithms and priority functions were investigated, a simple extension of the acyclic list scheduling algorithm and of the commonly used height-based priority function proved to be near-best in schedule quality and near-best in computational complexity.

To understand the intuition behind the algorithm, we resort to the view that we are, conceptually, scheduling the loop as we unroll it, with an eye to kernel recognition. What is different is that we shall be proactive in causing the repeating pattern, the kernel, to appear. We shall do so by enforcing two constraints upon the schedule that we create for the loop as we simultaneously unroll it.

- First, we shall insist that each iteration<sup>1</sup> begin exactly II cycles after the previous one.

- Second, each time we schedule an operation in one iteration, we shall tentatively schedule the same operation for subsequent iterations at intervals of II, even if it entails the unscheduling of other tentatively scheduled operations from subsequent iterations due to resource or dependence conflicts. However, when possible, each operation is scheduled so as to not unschedule any operation that was tentatively scheduled previously.

<sup>&</sup>lt;sup>1</sup> Note that an iteration at this point might correspond to multiple original iterations if the loop was pre-unrolled as discussed in Section 1. In terms of the original iterations, this constraint states that there is a periodic sequence of initiation intervals such that the length of one period is II.

Starting iterations at fixed intervals of II is similar to limiting the "span" [3] and the use of the pacemaker function [56] which ensure that, in the steady state, the average rate of starting iterations is equal to the average rate at which they finish so that a repeating pattern will form. One difference is that this constraint imposes the steady state rate right from the outset, thereby expediting the formation of the kernel. A further difference is that, although we enforce a regular rate of starting iterations, and one that is equal to the rate at which they complete, we place no constraints upon the number of iterations that might be executing simultaneously. As a result, it permits the necessary amount of "slip" to develop between operations. For instance, if operation B is scheduled more than 3\*II cycles later than operation A in the same iteration, then operation A is scheduled three times before B is scheduled for the first time.

The tentative scheduling of operations from subsequent iterations is the key difference with respect to other kernel recognition schemes. It provides guidance to the scheduler, when scheduling one iteration, as to what is desirable from the viewpoint of subsequent iterations in order to quickly achieve a repeating kernel. However, since it is only a tentative schedule, it does not block the forward progress of the scheduler in the event that the current operation cannot be scheduled because it conflicts with one or more operations from a subsequent iteration.

The result is that a repeating pattern, with a period of II, is enforced for the remainder of the schedule even at the expense of having only a partial schedule. If at any point, all operations from one iteration have been scheduled (without having to displace any tentatively scheduled operations from subsequent operations), then all operations from all subsequent iterations have, by construction, also been scheduled, and with a repetitive pattern. Thus, it is not necessary to explicitly check whether we have reached a previously visited state, i.e., kernel recognition becomes unnecessary. Retroactively, one can also reschedule operations from all previous iterations to conform to the schedule of the kernel. Now, because every iteration has the same schedule, staggered in time by II cycles, the repeating portion of the scheduled unrolled loop can be rolled up into a kernel with a loop around it, preceded by a prologue and followed by an epilogue.

Of course, in practice there is no need to actually unroll, schedule and then re-roll. The multiple iterations that unrolling algorithms schedule, are simulated in the case of modulo scheduling by repeatedly re-scheduling one II's worth of instructions on the MRT. One can view the iterative modulo scheduling process as consisting of sliding an II-long window down the code as it is unrolled and scheduled. In unroll-and-schedule terms, the MRT can be viewed as consisting the

1

last instruction of the schedule thus far (the current instruction) plus the next II-1 instructions that solely consist of tentatively scheduled operations. The rest of the schedule is tentatively the same as these last II instructions. The use of an MRT enforces both the constraint that a new iteration begin every II cycles and the constraint that all subsequent instances of an operation be scheduled at regular intervals of II. The iterative aspect of this modulo scheduling algorithm refers to the willingness, when necessary, to schedule an operation even at the expense of unscheduling a previously scheduled operation.

#### 4.2 The core algorithm for iterative modulo scheduling

The iterative modulo scheduling algorithm is shown in Figures 7, 8, 10 and 11. It assumes that two pseudo-operations, START and STOP, are added to the dependence graph. START and STOP are made to be the predecessor and successor, respectively, of all the other operations in the graph. Procedure ModuloSchedule (Figure 7) calls IterativeSchedule (Figure 8) with successively larger values of II, starting with an initial value equal to the MII, until the loop has been scheduled. IterativeSchedule looks very much like the conventional acyclic list scheduling algorithm [1, 41]. The points of difference are as follows.

- Acyclic list schedulers, typically, employ instruction scheduling. Although this is not

necessary, it is more natural for various reasons. In view of the fact that with iterative modulo

scheduling an operation can be unscheduled and then rescheduled, operation scheduling, rather

than instruction scheduling, is employed<sup>1</sup>. Also, the acyclic instruction scheduling notion that

an operation becomes "ready" and may be scheduled only after its predecessors have been

scheduled, has little value in iterative modulo scheduling since it is possible for a predecessor

operation to be unscheduled after its successor has been scheduled.

- The function HighestPriorityOperation, which returns the unscheduled operation that has the highest priority in accordance with the priority scheme in use, may return the same operation multiple times if that operation has been unscheduled in the interim. This does not occur in acyclic list scheduling. The priority scheme used, HeightR, is discussed in Section 4.3.

**,**\*

$<sup>^{1}</sup>$  Instruction scheduling operates by picking a current time and scheduling as many operations as possible at that time before moving on to the next time slot. In contrast, operation scheduling picks an operation and schedules it at whatever time slot is both legal and most desirable. Either style of scheduling can be used in iterative modulo scheduling, but the latter seems more natural.

```

procedure ModuloSchedule (BudgetRatio: real);

{ BudgetRatio is the ratio of the maximum number of operation scheduling steps }

{ attempted (before giving up and trying a larger initiation interval) to the }

{ number of operations in the loop. }

begin

{ Initialize the value of II to the Minimum Initiation Interval }

II := MII();

{ Perform iterative scheduling, first for II = MII and then for successively }

{ larger values of II, until all operations have been scheduled }