# HPL-PD Architecture Specification: Version 1.1

Vinod Kathail, Michael S. Schlansker, B. Ramakrishna Rau Compiler and Architecture Research HP Laboratories Palo Alto HPL-93-80(R.1) February, 2000 (Revised)

E-mail: {kathail, schlansk, rau}@hpl.hp.com

instruction-level HPL-PD is a parametric processor architecture conceived for parallelism, research in instruction-level parallelism (ILP). Its main purpose is to serve as a vehicle to investigate processor parametric architecture. architectures having significant parallelism and to investigate the compiler technology needed to effectively exploit such EPIC, VLIW, architectures. The architecture is parametric in that it admits superscalar, speculative machines of different composition and scale, especially with execution, respect to the nature and amount of parallelism offered. The VLIW predicated architecture admits EPIC. and superscalar execution, implementations so as to provide a basis for understanding the demerits of different programmatic merits and these styles of cache control. implementation. This report describes those parts of the architecture that are common to all machines in the family. It run-time introduces the basic concepts such as the structure of an memory disambiguation, instruction, instruction execution semantics, the types of branch register files, etc. and describes the semantics of the operation architecture repertoire.

Internal Accession Date Only

\* This is a revised version of "HPL PlayDoh Architecture Specification: Version 1.0" Technical Report HPL-93-80, February, 1994

<sup>©</sup> Copyright Hewlett-Packard Company 2000

# **1** Introduction

HPL-PD<sup>1</sup> is a parametric processor architecture conceived for research in instruction-level parallelism (ILP). HPL-PD defines a new philosophy of ILP computing, called Explicitly Parallel Instruction Computing (EPIC) [2-4], which represents an evolution of the VLIW architecture<sup>2</sup>. HPL-PD's main purpose is to serve as a vehicle to investigate processor architectures having significant parallelism and to investigate the compiler technology needed to effectively exploit such architectures.

When we released the first version of the architecture, we envisioned that a broad segment of the ILP research community would start using the architecture in their research, thus providing a single base to judge the merits of new architectural features and compiling technology. Since the publication of the first version, HP Labs and our university partners have been using the HPL-PD architecture for our own research. We, in conjunction with the University of Illinois' IMPACT project and NYU's ReaCT-ILP project, developed a set of tools, *e.g.*, a compiler and a simulator, for the HPL-PD architecture. In 1998, this compiler and simulation infrastructure, christened Trimaran<sup>3</sup>, was released to universities to encourage wide-spread research in EPIC architecture and compiler technology.

HPL-PD is a parametric architecture in that it admits machines of different composition and scale, especially with respect to the amount of parallelism offered. This is to enable experiments that answer one of the important question in ILP research—how much parallelism is available in programs and how best to exploit it. Although the architecture started out as a VLIW architecture and evolved into the EPIC architecture because of our research interests, it takes no position as to the style of implementation. It admits both EPIC (which includes VLIW as a subset<sup>4</sup>) and superscalar implementations so as to provide a basis for understanding the merits and demerits of the two styles of implementation. However, certain of HPL-PD's features are better motivated in the EPIC context.

We emphasize that the main purpose of the HPL-PD architecture is to serve as a research vehicle. Its current definition represents a collection of ideas whose merits we wish to explore and should not be taken as frozen in concrete. We expect the architecture to evolve. Its evolution will be engineered to support the investigation of important research questions in instruction-level parallelism. New features will be added as and when required, and subsets of interest will be defined for specific studies. We will ensure that the evolution takes place in a controlled manner and that it is coordinated with our collaborators.

<sup>&</sup>lt;sup>1</sup> This document is a revision of an earlier technical report published in 1994 [1]. In the intervening period, the name EPIC was coined to describe the style of processor architecture that was introduced in the earlier technical report. This document acknowledges the new name. Also, several new operations have been added to the operation repertoire.

$<sup>^2</sup>$  The Intel IA-64 instruction-set architecture [5] represents the first commercial instance of the EPIC style of architecture.

<sup>&</sup>lt;sup>3</sup> More information about Trimaran can be found at www.trimaran.org.

<sup>&</sup>lt;sup>4</sup> In the rest of this document, EPIC will be understood, implicitly, to include VLIW.

This report describes those parts of the architecture that are common to all machines in the family. It introduces basic concepts such as the structure of an instruction, instruction execution semantics, the types of register files, etc. and describes the semantics of the operation repertoire. The report is organized as follows. The rest of this section highlights the changes from the earlier version. Section 2 gives an overview of the architecture and discusses its parametric nature. It also discusses the EPIC and superscalar scheduling models. Section 3 discusses the instruction execution semantics including the semantics of multiple operations per instruction, speculative execution and predicated execution. Section 4 describes the data types and the types of the register files supported by the architecture. Section 5 introduces the format used for describing operations. The remaining sections except the last describe the operation repertoire provided by the architecture. Section 8 describes operations for data type conversion and for moving data between register files. Section 9 describes compare operations including compare-to-predicate operations. Section 10 describes the memory system and the load/store operation repertoire.

## **1.1 Architectural enhancements / changes in Version 1.1**

This sections highlights the new features as well the changes from the earlier version for readers who are already familiar with the earlier version of the architecture. The most visible change, of course, is the new name for the architecture. For various non-technical reasons, the architecture is now called HPL-PD. In addition, Sections 2.2, 3.1 and 3.2 have been modified substantially. We have also added a number of new references in order to bring them up-to-date.

Architectural enhancements in Version 1.1 are summarized below. These include several new integer, data conversion and move operations to allow greater experimentation. In addition, the architecture now provides a comprehensive set of load/store operations to save/restore and spill / unspill registers, something that was missing from the first version. Please note that we have added several new tables to accommodate the new operations, and thus, table numbers from the earlier version are not a good guide to look up the description of various operations in this version.

- 1. *Integer operations:* The architecture now includes five new integer operations -- ABS, MIN, MINL, MAX and MAXL. See Table 2 for their detailed specifications.

- 2. *Conversion operations:* Version 1.0 didn't include conversion operations between unsigned integers and floating point values. Thus, four new operations -- CONVLWS, CONVLWD, CONVLSW and CONVLDW, have been added for this purpose. Table 4 contains more details about these operations.

- 3. *Move operations:* The new version includes a number of new move operations. These include the following:

MOVEGBP, MOVEB, MOVEGCM, which are described in Table 5;

separate single and double precision moves between floating point registers, called MOVEFS and MOVEFD, which are described in Table 6;

MOVEGBGT, MOVEGBFT, MOVEGBPT, MOVEGBBT, which are described in Table 6; and

PRED\_CLEAR\_ALL, PRED\_CLEAR\_ALL\_STATIC, PRED\_CLEAR\_ALL\_ROTATING, which are described in Table 7.

Some of these operations are used in generating efficient code to spill or save/restore

predicate registers and speculative tag bits (see Section 10.7).

4. Load/store operations to spill and save/restore registers: Section 10.7 describes these operations as well as their typical usage. The new operations are: SAVE, RESTORE, FSAVE, FRESTORE, BSAVE and BRESTORE.

# **2** Overview of the architecture

The HPL-PD opcode repertoire, at its core, is similar to that of a RISC-like load/store architecture, with standard integer, floating point (including fused multiply-add type of operations) and memory operations. In addition, it provides a number of advanced features, which we believe are important for enhancing and exploiting parallelism in programs.

The first generation of VLIW machines, such as the Cydra 5 [6] and the Multiflow TRACE [7], proved themselves as very successful in exploiting the parallelism present in applications rich in counted loops (DO-loops). The results on "scalar" code were somewhat mixed. Apart from the use of speculative execution, there was very little ability to accelerate the execution of codes in which the limiting factor was not a shortage of execution resources but, rather, the critical path through the computation. There were few architectural features to assist in reducing the length of this critical path and, in fact, the absence of data caches served to exaggerate it. The primary objective with HPL-PD has been to provide architectural features that permit the relaxation of ordering constraints between operations on the critical path, thereby shortening the critical path and facilitating schedules that exhibit higher levels of ILP than are generally expected for such applications.

Many of the architectural features in HPL-PD have their microarchitectural counterparts in conventional or superscalar processors. In much the same way that the first generation of VLIW machines made the execution resources and latencies architecturally visible, HPL-PD makes these heretofore invisible capabilities visible to, and controllable by, the compiler. A case in point is the cache memory hierarchy that has generally been controlled entirely by hardware and transparent to the compiler. A consequence of this is that certain applications that have poor data locality suffer massive performance degradation because the hardware continues to use the same default cache management policy. Most high performance processors aimed at the scientific processing community have, as a consequence, avoided the use of a data cache. Unfortunately, sequential performance suffers in the absence of a data cache. HPL-PD addresses this dilemma by providing a cache hierarchy whose default behavior is to function in the conventional manner, but with the additional ability for the program to explicitly instruct the hardware on how to manage data which behaves anomalously.

In the first part of this section, we preview some of the more advanced features of the architecture. Then, we describe the parametric nature of the architecture.

### 2.1 Advanced features of the architecture

The advanced features of the architecture can be grouped into the following major areas. Many of these features are well-known in the ILP research community. The Cydra 5 [6], the Multiflow Trace [7] and the HP PA-RISC [8] architectures included several of these features. Some others have been proposed in the literature (see, for example, [9-15]).

1. Speculative execution: Speculative execution is an important technique for enhancing parallelism in a program. It is used to break certain types of dependences between

operations. Section 3.4 describes speculative execution in more detail and identifies two forms of speculation: control speculation used to move operations above branches and data speculation used in the run-time disambiguation mechanism discussed later.

The architecture supports speculative execution of most operations; exceptions are stores and branches. To correctly handle exceptions generated by speculative operations, the architecture provides speculative and non-speculative versions of operations and provides speculative tag bits on registers (see Section 4).

2. *Predicated execution*: Predicated or guarded execution refers to the conditional execution of operations based on a boolean-valued source operand, called a predicate. It is a way to enforce the requirements of program control-flow, which is different from that provided by branch operations. Predicated execution is often an efficient method to handle conditional branches and provides much more freedom in code motion than possible otherwise. Section 3.3 describes predicated execution in more detail.

To support predicated execution, the architecture provides 1-bit predicate register files and a rich set of compare-to-predicate operations which set predicate registers. In addition, most operations have a predicate input to conditionally nullify their execution (see Section 3.3 for exceptions).

- 3. *Memory system and load/store operations*: The architecture supports a hierarchical memory system consisting of first-level cache(s), a data prefetch buffer, second-level cache(s) and main memory. The main architectural features are:

- Compiler control of the memory hierarchy: The architecture provides latency and cache-control modifiers with load/store operations, which permit a compiler to explicitly control the placement of data in the memory hierarchy. The default, in the absence of the use of these directives, is the conventional hardware management. The architecture also supports prefetching of data to any level in the memory hierarchy.

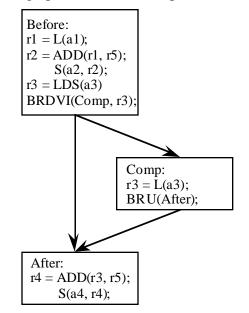

- Run-time disambiguation mechanism: "Maybe" dependences between store and load operations are a limiting factor in exploiting parallelism. The run-time disambiguation mechanism is used to break these dependences. It permits a load and dependent operations to be issued before potentially aliasing stores even in the absence of conclusive compile-time aliasing information. The mechanism consists of three related families of operations, called data speculative loads (LDS), data verify loads (LDV) and data verify branches (BRDV).

In addition, the memory operations in an instruction are executed in left-to-right prioritized order (see Section 3.2). This allows stores and dependent memory operations to be issued in the same cycle. Also, the architecture provides post-increment load/store operations similar to the ones in the HP PA-RISC architecture. For hardware efficiency, the architecture doesn't provide pre-increment load/store operations. Section 10 describes memory operations in more detail.

4. *Branch architecture*: The branch mechanism described in this report is a preliminary attempt to address the efficient implementation of branches in ILP machines. It permits different pieces of the information related to a branch to be specified as soon as they become available in the hope that the information can be used to reduce the adverse effect of the branch, *e.g.*, by prefetching instructions from the potential branch target.

Prepare-to-branch operations are used to specify the target address and the static prediction for a branch ahead of the branch point, typically initiating instruction prefetch. The architecture provides a separate type of register file, called a branch target register file, to store information about branches that have been prepared. Compare-to-predicate operations are used to compute branch conditions, which are stored in predicate registers. Branch operations test predicates and perform the actual transfer of control. The operation repertoire includes special branch operations to support software pipelining of loops. Section 11 describes branch architecture in more detail.

- 5. Unusual semantics for simultaneous writes to registers: The architecture permits multiple operations to write into a register simultaneously provided they all write the *same value*. In this case, the result stored in the register is simply the value being written. In the case of predicate registers, this atypical semantics is useful for efficient evaluation of boolean reductions (see below). In the case of other types of registers, the utility of this semantics is a research topic. See Section 3.2.

- 6. Support for efficient boolean reduction: We are interested in a class of parallelization techniques, which we generically call height-reduction of control dependences. In many cases, application of these techniques require a fast way to compute AND or OR of several boolean values to derive either a branch condition or a predicate to guard the execution of operations. The architecture provides a set of compare-to-predicate operations (OR and AND classes in Section 9.3) for efficient evaluation of boolean reductions.

- 7. *Register files*: The architecture supports rotating registers in integer, floating-point and predicate register files in order to generate "tight" code for software-pipelined loops. See Section 4.

### 2.2 Parametric nature of the HPL-PD meta-architecture

The EPIC philosophy is that it is the compiler, not the hardware, that is responsible for orchestrating the ILP of an executing program [4, 3]. The code for an EPIC processor reflects an explicit plan for how the program will be executed. This plan is created statically, i.e., at compile-time. It specifies when each operation will be executed, using which functional units, and with which registers as its operands. The EPIC compiler designs this plan, with full knowledge of the processor. The plan is communicated, via an instruction set architecture that can represent parallelism explicitly, to hardware which then executes the specified plan. The existence in the code of this explicit plan permits the EPIC processor to have relatively simple hardware despite high levels of ILP.

Static scheduling is necessary for superscalar processors as well, if the best performance is to be achieved at run-time. The definition of a good compile-time scheduling philosophy for superscalar processors is still an open problem. One strategy is to use the EPIC scheduling philosophy, an approach that has been adopted by the IMPACT project. After scheduling and register allocation, each parallel instruction is emitted as a series of sequential instructions. The superscalar hardware is expected to rediscover the parallelism at run-time and perform dynamic scheduling to achieve the intended ILP.

An EPIC code generator (the scheduler and register allocator) is responsible not just for the performance of the code, but for its correctness as well. Accordingly, it requires the following detailed information about the target EPIC processor [16]:

- 1. The register file structure. This includes the number of register files and, for each one, the number of registers in it and their bit width.

- 2. The operation repertoire. An *operation* consists of an opcode and a register tuple—one register each per operand. We treat any addressing modes supported by the target machine

as part of the opcode rather than as part of an operand. An operand is either a literal or a register in the target machine. For uniformity, we model a literal as the contents of a readonly "literal register". Multiple instances of an operation correspond to the presence in the machine of multiple functional units that can perform that operation. The operation repertoire specifies the opcode repertoire and, for each opcode, the sets of register files that it can access. Implicitly, and in a manner that is more directly useful to a compiler, this specifies the connectivity between the functional units and the register files.

- 3. Explicitly scheduled resources. This is the set of resources (functional units, buses, instruction fields, etc.) that the compiler must manage to ensure that two operations do not attempt to use the same resource at the same time.

- 4. The resource usage behavior of each operation. The compiler must use this information to ensure that the issue times of any two operations that use the same resource is such, relative to each other, that they will not end up using that resource simultaneously. This also determines which sets of operations can be issued simultaneously on this processor.

- 5. Latency descriptors. Every operation has a latency descriptor that specifies when, relative to the time that the operation is issued, each source operand is read and each destination operand is written.

HPL-PD is a meta-architecture, *i.e.*, a parametric processor architecture that encompasses a space of machines each of which has a different amount of ILP and a different instruction set architecture (ISA)<sup>5</sup>. Consequently, HPL-PD cannot be specific regarding all five types of information listed above. It only describes the first two, and in a manner that supersets the corresponding information for any specific ISA. In other words, HPL-PD (*i.e.*, this document) only describes the types of register files and the operation repertoire supported by the meta-architecture. Furthermore, the types of register files and the operation repertoire of any particular processor will be a subset, perhaps a proper subset, of what is defined in this document. Section 4 describes the types of register files supported by the architecture. Sections 6 through 11 describe HPL-PD's operation repertoire.

Architectures within the HPL-PD space consist of a set of register files, a set of functional units connected to register files, and a hierarchical memory system. A specific machine can have one or more of each type of register file except for the control register file<sup>6</sup>; there is exactly one control register file in each machine. Likewise, a specific machine can have one or more instances of each operation in HPL-PD's operation repertoire. Multiple instances of an operation means that multiple instances of that operation can be issued in parallel, *i.e.*, there are multiple functional units in the machine that can perform this operation.

All five types of information listed above, regarding the specific target processor, must be supplied to the compiler. A *machine-description database (mdes)* specifies this information to the compiler. The register file and operation repertoire information supplied in an mdes must be consistent with what is specified in this document. In collaboration with the University of

<sup>&</sup>lt;sup>5</sup> Although HPL-PD is, strictly speaking, a meta-architecture, for convenience we shall refer to it as an architecture.

<sup>&</sup>lt;sup>6</sup> We call a machine with one register file of each type a *single-cluster* machine, and a machine with more than one register file of at least one type a *multi-cluster* machine. Our focus has been on single-cluster machines; thus, it is possible that certain issues about multiple-cluster machines have not been properly addressed in this report.

Illinois' IMPACT project, we have developed an approach to describe an EPIC machine to a compiler [17, 18]. It was designed with the EPIC scheduling philosophy in mind and is based on the approach used by Cydrome in its compiler. The approach is supported by the following facilities:

- 1. A high-level machine description language: This is a human-readable version of the five types of information listed above.

- 2. A low-level machine description language: It specifies the same information as the high level machine description language but in a form that is suitable as an input to a compiler.

- 3. A macro processor and translator from the high-level machine description to the low-level machine description.

- 4. The *mdes Query System* (mQS): This consists of the internal mdes data structures that hold the above information, and an associated query interface. The query interface is a collection of interface functions that a compiler can call to get the requisite information about the target machine and to manage a resource-usage map during scheduling.

A more detailed discussion of these topics is beyond the scope of this report. Interested readers should refer to the detailed description of the structure of the machine description database and the underlying theory presented in [16]. This paper describes an incremental model of code generation for EPIC processors that provides an efficient way to generate high quality code. The paper also relates this process to the structure of the machine description database that is queried by the code generator for the information that it needs about the target processor. A companion document [18] discusses an implementation of these ideas and techniques in Elcor, which is our compiler research infrastructure.

Elcor is a part of the Trimaran infrastructure. Trimaran, too, is designed such that it is parametric in nature. It reads the architectural parameters for a machine from its mdes. Thus, the various components of Trimaran will work either with all machines in the HPL-PD space or with a well-defined subclass, *e.g.*, EPIC machines.

The information discussed above is adequate for experiments that concern themselves with scheduling, register allocation and performance as a function of the parallelism and cost of the processor's datapath. For such purposes, the details of the instruction format are unimportant. However, if the issues under investigation are code size, scheduling that is sensitive to code size, instruction cache performance or instruction unit complexity and cost, then detailed knowledge of the instruction format is essential.

The components of the compiler infrastructure that depend upon this information are the assembler, the disassembler and the debugger. In keeping with the spirit of the rest of the infrastructure, it is desirable that they, too, be parametric and machine description driven. The nature of the description of the instruction format depends on the nature of the instruction format, for which there are many alternatives [5, 4]. The class of instruction formats that we have selected for our EPIC research is the class of what we term multi-template instruction formats [19]. We have also defined a strategy for dealing with instruction formats in a parametric fashion [20]. It consists of the following components:

- 1. A meta-grammar and meta-syntax for the class of multi-template instruction formats. The syntax of the instructions (i.e., the instruction format) for any given processor is a sentence of this meta-grammar.

- 2. An internal data structure, the Instruction Format Tree (IF-tree), for representing the description of an instruction format within the mdes.

3. A set of mQS interface functions that are needed during assembly and disassembly.

Our implementation of this strategy in Elcor is partially complete. When finished, it will be similar to the one described above, that is, there will be a high-level language for describing a multi-template instruction format, a low-level machine-readable counterpart, a translator from the high-level to the low-level description, and extensions to the internal mdes data structures and the query interface.

Even for experiments that do not require knowledge of the detailed instruction format, the compiler must still be able to specify branch addresses for the simulator's benefit. In such cases, one can assume an abstract machine whose program counter counts in units of an operation, *i.e.*, an operation's address is the number of operations preceding it in the program text, as laid out in memory. A point to note is that branch addresses must point to instruction boundaries; it is illegal to branch into the middle of an instruction.

# **3 Execution semantics**

This section describes the basics of instruction execution. Sections 3.1 and 3.2 describe the logical structure of an instruction and the execution semantics of an instruction, respectively. Section 3.3 describes predicated execution, and Section 3.4 covers speculative execution. The last section contains brief comments about exceptions and exception handling in the case of normal execution of operations.

## **3.1 Logical instruction structure**

In this section, we describe those aspects of the instruction structure that are necessary to understand HPL-PD. Since our discussion of HPL-PD is not, and cannot be, tied to any specific instruction format, we shall operate at what might, conceptually, be viewed as the assembly language level. Accordingly, we define a simple assembly language to facilitate our description of HPL-PD. This, or some equivalent syntax, would also be suitable as input to a simulator.

An *instruction* consists of a sequence of operations, each of which is terminated by a delimiter (a semi-colon). Each instruction is terminated by an end-of-instruction marker (the new line). The end-of-instruction marker can be viewed as a pseudo-operation, which performs actions typically associated with the end of an instruction, *e.g.*, advancing the program counter and advancing virtual time. For the convenience of a simulator, branch operations appear as the last operations within an instruction. There is no explicit NOP instruction in our assembly language. An empty instruction, *i.e.*, an instruction with no operations, serves the same purpose as a NOP.

In the superscalar version of the architecture, an instruction has zero operations (*i.e.*, a NOP) or one operation. In the EPIC version, the maximum number of operations in an instruction, the maximum number of operations of a specific type (e.g., integer operations or memory operations), and the legal combinations in which they may appear are all specified by the mdes.

An *operation* corresponds to an elementary operation performed by a functional unit, *e.g.*, an add or a load. An operation specification consists of the following:

- 1. An opcode: Related opcodes are grouped into a family. Each family of opcodes has a major opcode and a set of modifiers. An opcode consists of a major opcode and a specific value for each of the modifiers associated with the family.

- 2. A list of sources: A source is either a register specifier or a literal. Conceptually, each register file in a machine has an unique name, and a register specifier consists of the name

of a register file and a register number within the register file. Literals are discussed below.

3. A list of destination register specifiers. Note that there are no destinations in the case of store operations and some of the branch operations.

The architecture permits integer literals in an operation. An operation that expects an integer value as an operand can specify either an integer register or an integer literal. Note that a machine can currently have literals of only one width: 32 bits<sup>7</sup>. Note, also, that there is no support for floating-point literals.

In this report, we use the following notations. An opcode is of the form a.b.c.d where a is the major opcode and b, c, d are modifiers. Modifiers are written in the same order in which they appear (top to bottom) in tables. In addition, the speculative version of an opcode is denoted by the modifier "E", which always appears at the end. The notation for writing register specifiers is as follows. Consider a register file named "R" containing  $n_s$  static registers and  $n_r$  rotating registers (see Section 4). Then, we specify a *static register* within the file as Ri where i is in the range  $0 \le i \le n_s - 1$ , and specify a rotating register as R[j] where j is in the range  $0 \le i \le n_r - 1$ . In some cases, we use a, b, c, etc., for register specifiers; their meaning will be clear from the context. The following example illustrates the notation used in writing assembly code.

| Cycle | Instruction                                                |

|-------|------------------------------------------------------------|

| 1     | GPR1 = ADD.W(GPR2,GPR3); $GPR4 = SUB.W(GPR2,GPR3)$ if PR2; |

| 2     |                                                            |

| 3     | FPR2 = FADD.S(FPR1, FPR3); BRU(BTR2);                      |

In this example, there are three instructions, each of which is on a separate line. The first instruction contains two operations; the second instruction is an empty instruction, which is denoted by ----; and the third instruction again contains two operations, one of which is an unconditional branch (BRU). The number in the cycle column indicates the cycle number in the program's virtual time when the corresponding instruction is issued. For example, the third instruction is issued at the third cycle in the program's virtual time. In some cases, when cycle numbers are not shown explicitly, they are assumed to be sequentially numbered.

To understand the notation used for writing operations, consider the first operation in the first instruction. ADD.W is its opcode, general-purpose registers GPR2 and GPR3 are its sources, and the general-purpose register GPR1 is its destination. If necessary, the guarding predicate for an operation is specified after the keyword "if"; for example, see the second operation in the first instruction. Each operation is terminated by a ";" delimiter.

# **3.2 Instruction execution**

As mentioned in the introduction, we deliberately do not take a position about the style of implementation and admit both EPIC and superscalar implementations of HPL-PD. Broadly speaking, the characteristics of these two models of execution semantics are as follows.

<sup>&</sup>lt;sup>7</sup> We recognize this as a major shortcoming of HPL-PD. It will be rectified in the next revision of this document, which will articulate a flexible way to define literals of various widths via the mdes.

The EPIC model [4, 3] is characterized by the following: MultiOp instructions and architecturally visible, non-unit assumed latencies (NUAL) for operations. EPIC code cannot be interpreted correctly without an understanding of these two features. The term MultiOp means that an instruction may explicitly indicate that multiple operations are to be issued in parallel. Within the EPIC model, we can identify two types of machines: "equals" (EQ) machines and "less-than-or-equals" (LEQ) machines. In an EQ machine, the latency(s) associated with an operation defines the exact time when the operation produces its output(s). In a LEQ machine, the latency(s) associated with an operation defines only the latest time by which the operation produces its output(s); the operation may produce its output(s) earlier than that. HPL-PD permits both types of machines. A detailed discussion of the merits of each type is beyond the scope of this report.

The superscalar model is characterized by the following. Instructions are UniOp, i.e., they have exactly one operation (which could be a NOP operation), operations have unit assumed latency (UAL), and dynamic scheduling is used to issue operations in parallel. That is not to say that static scheduling is not useful or that operations actually have unit latency. For performance reasons, compilers for superscalar machines, too, will schedule operations with full knowledge of the amount of parallelism in the machine and the actual latencies of operations. However, this knowledge is not necessary to correctly interpret code generated for a superscalar processor.

The number of instructions issued in a single cycle depends upon the implementation. In the typical EPIC version of the architecture, a single instruction is issued in each cycle. However, the architecture permits dynamically scheduled EPIC machines in which more than one instruction can be issued in a single cycle [21]. In the superscalar version, the number depends upon the capabilities of the dynamic scheduling hardware in a machine.

The execution semantics of a Multiop instruction is as follows. All operations in an instruction can be issued in parallel. Consequently, there can be no flow (*i.e.*, read-after-write) dependences between operations in a HPL-PD instruction with one notable exception. The architecture permits flow dependences between memory operations as long as they go from left-to-right in an instruction by ensuring that the following holds:

• The memory operations within an instruction are executed in an order that is consistent with their sequential left-to-right order of execution. This permits compilers to reduce the length of critical paths involving memory operations. For example, two store operations, one of which potentially depends upon the other, can be issued in the same instruction. Similarly, a store and a flow-dependent load can also be issued in the same instruction.

The semantics described above for a Multiop instruction permit two variations [4]. The first variation, called *Multiop-P* semantics requires that the correct execution is guaranteed only if all the operations in the instruction are issued simultaneously. The compiler can schedule code with the assurance that all operations in one instruction will be issued simultaneously. For instance, it can even schedule two mutually anti-dependent copy operations, which together implement an exchange copy, in the same instruction. Without this assurance, the exchange copy would have had to be implemented as three copy operations that require two cycles. Thus, the Multiop-P semantics permits admissible dependences between operations (*i.e.*, anti and output dependences) to be bi-directional across the instruction.

However, MultiOp-P semantics pose a problem with respect to the compatibility across a family of machines with differing amount of functional units. When code that was generated for a machine with a certain width (*i.e.*, number of functional units) has to be executed by a narrower machine, the narrow processor must necessarily issue the MultiOp instruction semi-sequentially,

one portion at a time. Unless care is taken, this will violate MultiOp-P semantics and lead to incorrect results. For instance, if the aforementioned copy operations are issued at different times, the intended exchange copy is not performed.

The other variation, called *MultiOp-S* semantics, simplify sequential execution by excluding bidirectional dependences across a MultiOp instruction. MultiOp-S instructions can still be issued in parallel, but they can also be issued sequentially from left to right. This permits the code compiled for a wide machine to be correctly executed on a narrow machine. On the other hand, the Multiop-S semantics excludes some of the benefits of the Multiop-P semantics. For example, an exchange-copy cannot be implemented as two copy operations in the same instruction. The compiler must ensure that admissible dependences between operations in a MultiOp instruction are only from left to right.

MultiOp-P and MultiOp-S bear similarities to EQ and LEQ, respectively. Both MultiOp-P and EQ guarantee that operations will not complete early in virtual time, whereas MultiOp-S and LEQ permit it. Although it need not necessary be the case, one would tend to use MultiOp-P in conjunction with EQ semantics, and to pair MultiOp-S with LEQ.

At present, the Elcor compiler in Trimaran supports only the Multiop-S semantics. It provides several versions of Multiop-S, which differ in the set of operations that are allowed to have intra-instruction dependences. For example, one version doesn't permit any intra-instruction dependences; another allows intra-instruction dependences only among memory operations.

The execution of an operation involves reading its inputs, computing the specified function and writing the results into the specified destination registers. The detailed timing constraints concerning the execution of an operation, *e.g.*, the latency of the operation, the times when inputs are sampled, the times when outputs are produced, are architectural parameters specified separately for each machine in its mdes.

The architecture provides unusual semantics for simultaneous writes to registers. Multiple operations may write into a register in a cycle provided they all write the *same value*. In this case, the result stored in the register is simply the value being written. On the other hand, if multiple operations attempt to write different values into a register simultaneously, then the result stored in the register is undefined. In the case of predicate registers, this atypical semantics is useful for efficient evaluation of boolean reductions; see the description of compare-to-predicate operations in Section 9.3. The utility of this semantics in the case of other types of registers such as general-purpose and floating-point registers is not well-understood. The full generality is provided to facilitate research in this area.

The architecture permits multiple branch operations in an instruction. Moreover, the latency of a branch operation is an architectural parameter that is specified for each machine in its mdes. A significant point to note is that a branch takes effect after exactly n cycles where n is the latency of the branch. That is, branch operations always have the "equals" semantics, even in "less-than-or-equals" machines.

Like integer or floating point operations, branch operations are executed in a parallel pipelined manner with the following implications. First, consider the execution of an instruction containing multiple branch operations. In this case, the result is well-defined only when at most one operation takes the corresponding branch. If more than one branch operations specify that the corresponding branches be taken, then the result of the execution is undefined. In other words, simultaneous multiple writes to the program counter (PC) are not permitted. It is the compiler's responsibility to ensure that, in an instruction, at most one branch takes. Second, branch

operations in the delay slots of a branch are executed in a pipelined fashion, which may give rise to "visits" (see Section 11).

#### **3.3 Predicated execution**

Predicated or guarded execution is a way to enforce the semantics of program control-flow, which is different from the one provided by branch operations. It refers to the conditional execution of operations based on a boolean-valued source operand, called a predicate. Predicated execution is frequently an efficient method to handle conditional branches and provides much more freedom in code motion than possible otherwise. For example, a compiler can use predicated execution to eliminate many of the conditional branches present in a program, a technique commonly referred to as *if-conversion*. If-conversion not only reduces the impact of branch latencies but has the benefit that operations can be moved freely across branch boundaries. If-conversion is used in software-pipelining of loops with conditionals [22] and in hyperblock scheduling [23]. Predicates may also be used to fill branch delay slots more effectively than possible otherwise. Note, however, that predicated execution is no substitute for branching. Its benefits are obtained at a price--operations that are nullified still consume machine resources in the EPIC model of execution. The Cydra 5 architecture [6] included a general form of predicated execution. Other architectures with some form of conditional execution include HP PA-RISC and DEC Alpha.

The model of predicated execution in the HPL-PD architecture is an enhanced version of the one provided by the Cydra 5 architecture. The architectural features relevant to predicated execution are as follows:

- 1. There are 1-bit predicate register files, which are partitioned into static and rotating portions (see Section 4).

- 2. The main operations on predicate registers are a set of compare-to-predicate operations, each of which can set up to 2 predicate registers. There are also operations to move data between predicate registers and integer registers and operations to clear predicate registers *en masse*. In addition, all of the integer computation operations and standard load/store operations can be used to operate on 32 predicates at a time by using control register aliases (see Section 4).

- 3. A class of compare-to-predicate operations and the unusual semantics of simultaneous writes to registers described in Section 3.2 provide an efficient method to evaluate boolean reductions. This provides an effective method for control-height reduction.

- 4. Most operations have a predicate input that guards their execution. We call such operations *predicated operations*. When the predicate has value 1 (true), the operation executes normally. When the predicate has value 0 (false), the execution of the operation is nullified *i.e.*, no change in the machine state takes place. The exact mechanism by which the execution of an operation is nullified depends upon the implementation. Predicated operations can be executed unconditionally by specifying the static predicate register PR1, which is permanently 1 when used as an input (see also Section 4.5).

There are a few operations whose execution cannot be nullified. These operations also have one or more predicate inputs, but they use these inputs like data inputs. Branch operations related to software-pipelining of loops fall in this category. Compare-to-predicate operations are also an exceptional case for which it is hard to classify whether they are predicated or not (see Section 9.3 for more details).

## **3.4 Speculative execution**

The architecture supports speculative execution of most operations; the exceptions are stores to memory and branch operations. Some of the architectural support for speculative execution is similar to the one described in [14]; see also[11, 15].

In this report, we use the term speculative execution in a broader sense than it is used in the literature. The notion of speculative execution includes two distinct forms of speculation.

- 1. *Control speculation*: This refers to the execution of operations before it has been determined that they would be executed in the normal control-flow of execution. Traditionally, speculative execution has been identified with control speculation.

- 2. *Data speculation*: This refers to the execution of operations with potentially incorrect operand values. An example of the data speculation is the execution of both a load and an operation that uses the loaded value before potentially aliasing stores that originally preceded them. The operation that uses the loaded value may execute with incorrect data. In the case of data speculation, the compiler must ensure program correctness by creating a code sequence, which is invoked to re-issue the operations that were executed with incorrect data. The run-time disambiguation mechanism described in Section 10.6 provides a form of data speculation.

The main issue in both forms of speculation is the correct handling of *architecturally visible* exceptions. If a speculatively executed operation generates such an exception, then the exception should be deferred and reported only after it has been determined that the exception would also occur in the normal program execution.

To support exception handling, the architecture provides speculative tag bits on registers and provides speculative and non-speculative versions for most operations except for store and branch operations, which don't have speculative versions. We use the modifier "E" (for eager) to denote the speculative version of an operation; that is, the name for the speculative version is obtained by appending E to the name of the non-speculative counterpart. A couple of additional points to note are as follows. First, we assume that both speculative and non-speculative version of an operation behave identically with respect to the types of exceptions generated and the conditions under which they are generated. Second, we defer all issues related to the processing of exceptions for non-speculative operations to a later version of the architecture.

In order to clearly explain speculative execution, we introduce terms for generating and signaling an exception. Generation is the detection and logging of an exception condition resulting from the execution of an operation. A generated exception causes an exception signal when it is known that the operation would have executed in the original non-speculative code sequence. Exception signaling causes the CPU to treat an exception condition by invoking exception processing, which may result in abnormal program termination, invoking an exception handler, or other special actions.

Prior to any speculative code motion, exception generation and signaling are simultaneous. Speculative code motion may separate the exception generation and signaling times using the speculative tag bit to propagate the exception condition from an operation which generates the exception to an operation which signals the exception. This allows an operation to execute speculatively and generate but not signal an exception. The exception is signaled only if it is determined later that the operation would have also executed in the original program. The means by which this is accomplished is described below.

*Execution of a speculative operation*: If the speculative tag of every source register is not set, then the execution proceeds normally when the operation doesn't generate an exception. When the operation does generate an exception, the speculative tag of the destination register(s) is set. If the speculative tags of one or more source register are set, then an exception propagation occurs. The operation simply sets the speculative tag bit of its destination register.

To report an exception, the value of PC and any other required state information at the time of the exception must be recorded and propagated. This report doesn't describe the mechanism for doing this; that is left for a later version of the report. (We will probably use an extension of the mechanism described in [14]. The main complication is that predicates are 1-bit registers.)

*Execution of a non-speculative operation*: If the speculative tag of every source registers is not set, then the execution proceeds normally, and any exception generated by the operation is immediately signaled. If the speculative tags of one or more source registers are set, then it indicates that an exception was generated by a speculative operation. The exception is, therefore, signaled using the recorded state information. If multiple source registers have their speculative tag bit set, the exception corresponding to the first operand is reported.

Table 1 summarizes the handling of exceptions; a --- indicates that the corresponding value is undefined. (For instance, the IEEE floating-point standard requires that the destination of an excepting instruction be left unchanged.)

| Operation type      | Tag bits of source registers | Operation<br>generates an<br>exception | Destina-<br>tion's tag<br>bit | Other actions                                                       | Signal<br>exception if<br>enabled |

|---------------------|------------------------------|----------------------------------------|-------------------------------|---------------------------------------------------------------------|-----------------------------------|

| Speculative         | 0 for all sources            | No                                     | 0                             | Update destination register with the result                         | No                                |

|                     |                              | Yes                                    | 1                             | Record PC and other state<br>information for exception<br>reporting | No                                |

|                     | 1 for one or<br>more sources | Don't care condition                   | 1                             | Record that an exception was propagated                             | No                                |

| Non-<br>speculative | 0 for all sources            | No                                     | 0                             | Update destination register with the result                         | No                                |

|                     |                              | Yes                                    | 0                             |                                                                     | Yes                               |

|                     | 1 for one or<br>more sources | Don't care condition                   | 0                             |                                                                     | Yes                               |

**Table 1:** Semantics of speculative operations

# 3.5 Exceptions and exception handling for non-speculative operations

A detailed description of all issues related to exceptions and exception handling for nonspeculative operations are left to a later version of the architecture. These issues include the types of exceptions generated by an operation, conditions under which they are generated, masking of exceptions, and the exception handling mechanism. The only point we would like to emphasize is the one related to speculative execution. That is, a non-speculative operation also signals an exception when the speculative tag of any of its source registers is set.

# **4 Register files**

This section describes the data types and the types of register files supported by the architecture. Section 4.1 describes the data types; Section 4.2 comments on static and rotating registers; the remaining sections describe the various types of register files.

A machine in the HPL-PD family can have one or more register files of each type except for the control register file; each machine contains exactly one control register file. The number of register files of each type and the number of registers in each file are architectural parameters, which are specified separately for each machine. We assume that each register file in a machine has a unique name and that a register specifier consists of a register file name and a register number within the file.

## 4.1 Data types

The data types supported by the architecture are byte, integer, floating-point number and predicate. The first three data types and their formats are the same as in HP PA-RISC.

- Byte: Bytes are signed or unsigned 8-bit quantities and are packed four to a word. They may be used to represent signed values in the range -128 through 127, unsigned values in the range 0 through 255, an arbitrary collection of 8 bits, or an ASCII character.

- Integer: There are signed and unsigned integers in two lengths: half-word (16 bits) and word (32 bits). 64-bit integers will be included in a later version. Half-word integers must be aligned at two-byte boundaries, *i.e.*, they must be stored in memory at addresses evenly divisible by two. Word integers must be aligned at four-byte boundaries. Note that unsigned integers can also be used to represent an arbitrary collection of 16 or 32 bits.

- Floating point: There are IEEE compliant 32-bit single precision and 64-bit double precision formats for floating point numbers. Single precision numbers must be aligned at four-byte boundaries, and double precision numbers at eight-byte boundaries.

- Predicate: 1-bit boolean values

# 4.2 Static & Rotating Registers

The architecture supports both static and rotating registers. Most register files (see the following sections) are partitioned into static and rotating portions with differing numbers of registers. The static registers are conventional registers; the rotating registers logically shift in register address space every time the rotating register base (RRB) is decremented by certain loop-closing branches; see Section 11.2.5.

Rotating registers have the special property that the register state prior to rotation is closely related to the register state after rotation. Consider a register file R with  $n_r$  number of rotating registers; that is, the file contains registers R[0] ... R[ $n_r$  - 1]. Assume that x is the value contained in some register R[j] prior to a "rotate" operation where j is in the range  $0 \le j \le (n_r - 2)$ . Then after a rotate operation R[j +1] has value x. Thus, for example, if R[0] has value x prior to rotation then R[1] has value x after a single rotation. Note that the value of R[0] after rotation is unspecified. We call this an *open loop* model of rotation, *i.e.*, there is a contiguous window of size  $n_r$  into a circular register file of unspecified size. This simplifies the definition of architectural families of processor with varying numbers of rotating registers in a file and provides better code compatibility across the family.

Typically, rotating registers are implemented in terms of a rotating register base (RRB), which is used to map register offsets to physical registers. A register access involves the modulo sum of the register offset to RRB in order to select a physical register. That is,

```

register address = (register offset + RRB) mod n_p

```

where  $n_p$  is the number of physical registers and  $n_p \ge n_r$ . Rotation is accomplished by simply decrementing the RRB. In such an implementation, precisely in the case where the number of physically addressed rotating registers is equal to  $n_r$ , we have a *closed loop* model. That is, if  $R[n_r - 1]$  has value x prior to rotation, then R[0] has value x after rotation. We constrain code generation schemes to make no use of this fact and thus allow the number of physical registers, in general, to differ from  $n_r$ . In the rest of this report, we will assume the above implementation of rotation.

# 4.3 General purpose register file (GPR):

It is used to store signed or unsigned integers and has the following properties:

- Width = 32 bits + 1 bit for speculative tag.

- Partitioned into static and rotating portions.

By convention, static GPR0 is used as a bit-bucket.

## 4.4 Floating-point register file (FPR):

It is used to store single or double precision floating-point values, and its characteristics are as follows:

- Width = 64 bits + 1 bit for speculative tag

- Partitioned into static and rotating portions.

- Static FPR0 = 0.0, static FPR1 = 1.0.

- Writes to static FPR0 and FPR1 are ignored.

### 4.5 Predicate register file (PR):

It is used to store predicates and has the following properties:

- Size = 1 bit + 1 bit for speculative tag.

- Partitioned into static and rotating portions.

- Static PR0 = 0 (*i.e.*, false), static PR1 = 1 (*i.e.*, true).

- Writes to static PR0 and PR1 are ignored.

### 4.6 Branch-target register file (BTR):

This register file is used to store information about branches that have been prepared. The information for each prepared branch includes the branch target address and its static prediction.

- Size = 64 bits.

- 32 bit branch address + 1 bit for static prediction + 1 bit for speculative tag

# 4.7 Control register file (CR):

A machine in the HPL-PD family has exactly one register file of this type. Control registers provide a uniform scheme to access internal state within the processor. All integer operations can operate with control registers either as sources or as destinations. However, some of the operations may not make any sense on some of the control registers. We describe the registers in the control register file using mnemonics such as PC. The mapping of these mnemonics to actual register number in the control register file is part of a machine's description.

- Size = 32 bits.

- Control registers supported by the architecture are listed below.

- PC: Instruction Counter

- PSW: Processor status word

- RRB: Register Relocate Base for rotating registers

- LC: Loop counter

- ESC: Epilog stage counter

- PV(i, j): Aliases used to refer to 32 predicate registers at a time in a predicate register file. The first index identifies a register file, and the second index identifies a group of 32 registers in the file. For example, PV(1, 0) refers to the first 32 predicate registers in the predicate register file with name 1, PV(1, 1) to the second 32 registers in the same file, etc.

- IT(i, j), FT(i, j), PT(i, j): Aliases used to refer to 32 speculative tag bits at a time in a general-purpose register file, a floating-point register file and a predicate register file, respectively. The first index identifies a register file, and the second index identifies a group of 32 tag bits in the file.

- BTRL(i, j), BTRH(i, j): Aliases used to refer to low order 32-bits and high order 32 bits of a branch target register. The first index identifies a branch target register file and the second index identifies a register in that file.

# **5** Format of operation description

In the tables given in the subsequent sections, each row describes a single operation or a set of related operations. The description in each row consists of the following:

- Opcode: This specifies opcodes for the set of operations. It consists of a major opcode and a set of modifiers. The major opcode and each of the modifier sets are on separate lines. Each modifier consists of a set of mutually exclusive alternatives, separated by |. For example, the opcode for floating-point add operation is of the form:

- FADD S | D

This means that there are two floating-point add operations, one for single-precision (specified by S) and one for double-precision(specified by D). In some cases, there is only one alternative for a modifier, and the modifier may seem unnecessary. The reason for including such a modifier is to provide an easy way to add more alternatives in the future.

Section 3.1 describes the notation we use in this report for writing operation names. Note that the opcodes given in this column are for non-speculative versions. As described in Section 3.1, the opcode for the speculative version of an operation is derived by appending the modifier "E" to the corresponding non-speculative opcode. The Sp field described later indicates whether the architecture provides speculative versions for these operations or not.

- Operation description: This is a short description of the functionality provided by the major opcode and modifiers.

- I/O description: This is used to describe the following aspects of operations in the family. First, it provides a stylized description of the information about the register files from which the operation reads its *explicitly specified* operands and to which it writes its *explicitly specified* results. Second, it establishes an ordering on the sources and destinations, which is used in describing the semantics. Third, it is used to specify whether operations in the family are predicated or not.

The format of the I/O description is as follows:

• <predicated> <source>, ..., <source> : <destination>, ..., <destination>

The first term <predicated> is either P? or empty with the following interpretation:

- P?: This denotes that operations in the family are predicated. That is, they take a predicate register (static or rotating) as an input which is used to conditionally nullify the operation.

- An empty field (*i.e.*, no P?) denotes that operations are not predicated, that is, they don't have a predicate input that is used to guard their execution.

<source> or <destination> is a sequence consisting of one or more of the following:

- I: General purpose register (static or rotating)

- F: Floating point register (static or rotating)

- P: Predicate register (static or rotating). The corresponding predicate input/output is treated like a data input/output.

- B: Branch target register

- L: Integer literal. This cannot be part of a <destination> sequence.

- C: Control register

Thus, for example, ICL as a <source> specifies that the operand can be an integer register, a control register or an integer literal.

- Sp: Y(es) in this field indicates that these operations have both speculative and non-speculative versions. N(o) in this field indicates that there are no speculative versions of these operations.

- Opcode semantics: This describes the action performed by operations in the family using a C like syntax. In some cases, this field simply refers to the text. For predicated operations, the action specified in this field corresponds to the case when the predicate input is 1 (true).

It is implicit in the specification that when the predicate input is 0, then the execution of operation is nullified.

In the semantic description of operations, we use the following notation. Src<n>, for  $<n> \ge 1$ , denotes the n<sup>th</sup> source operand excluding the guarding predicate (if there is one). Similarly, dest<n>, for  $<n> \ge 1$ , denotes the n<sup>th</sup> destination. For predicated operations, the guarding predicate is denoted by src0. For operation that are not predicated, src0 has no meaning.

In describing operations, we don't enumerate cases under which an operation generates exceptions. As mentioned in Section 3.4, all issues related to exceptions are left for a later version of the architecture.

# **6** Integer computation operations

The operation repertoire includes a relatively standard set of arithmetic and logical operations on integers; see Table 2 on the next page. All these operations operate on 32-bit words; there are no byte and half-word operations. Arithmetic operations come in two forms: signed and unsigned. In this report, unsigned operations are distinguished by the word "logical" in their descriptions.

All integer operations can be issued speculatively and have a predicate input to guard their execution. Each operation includes the length (or format) specifier, which seems unnecessary given that there is only one option, *i.e.*, W. It is included so that the operation repertoire can be easily extended to support both 32-bit and 64-bit integers in the future.

The repertoire includes opcodes for complex operations like multiply, divide, remainder, min and max. They may be provided in hardware or emulated in software. Shift and add logical operations are useful in address computation, which typically involves multiplying by a small constant.

| Opcode     | Operation description  | I/O description  | Sp | Opcode semantics        |

|------------|------------------------|------------------|----|-------------------------|

| ABS<br>W   | Absolute value<br>word | P? ICL : IC      | Y  | dest1 = abs(src1)       |

| ADD<br>W   | Add<br>word            | P? ICL, ICL : IC | Y  | dest1 = src1 + src2     |

| ADDL<br>W  | Add logical<br>word    | P? ICL, ICL : IC | Y  | dest1 = src1 + src2     |

| AND<br>W   | AND<br>word            | P? ICL, ICL : IC | Y  | dest1 = src1 & src2     |

| ANDCM<br>W | AND complement<br>word | P? ICL, ICL : IC | Y  | dest1 = src1 & (! src2) |

| DIV<br>W   | Divide<br>word         | P? ICL, ICL : IC | Y  | dest1 = src1 / src2     |

| DIVL<br>W  | Divide logical<br>word | P? ICL, ICL : IC | Y  | dest1 = src1 / src2     |

**Table 2:** Integer computation operations

| Opcode                                                                                                 | Operation description                                                                                                                                                                                                               | I/O description                                                                                                                                                                                                                                      | Sp                              | Opcode semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX                                                                                                    | Maximum value                                                                                                                                                                                                                       | P? ICL, ICL : IC                                                                                                                                                                                                                                     | Y                               | dest1 = max(src1, src2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| W                                                                                                      | word                                                                                                                                                                                                                                | 1.102,102.110                                                                                                                                                                                                                                        | -                               | (), (), (), (), (), (), (), (), (), (),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |